# Vertical Bipolar Transistors in Laser-Recrystallized Polysilicon

J. C. STURM, STUDENT MEMBER, IEEE, AND J. F. GIBBONS, FELLOW, IEEE

Abstract—Vertical bipolar n-p-n transistors with a base width of 0.2  $\mu m$  have been fabricated in laser-recrystallized polysilicon films on thermally oxidized silicon substrates. With proper hydrogen annealing steps, common-emitter current gains on the order of 100 were possible. Recombination in the base-emitter space-charge region was found to be the dominant source of base current.

# I. INTRODUCTION

O DATE, almost all work in laser-recrystallized films has been with majority-carrier devices, i.e., MOSFET's. This is not surprising considering the inherent suitability of a thin film to the MOSFET structure. However, silicon-on-insulator (SOI) films have potential for bipolar transistors as well. An SOI bipolar transistor could have a lower collector-substrate capacitance than a conventional transistor and the isolation for a complementary process would be greatly simplified. Due to a high drive capability and the ability to sense low currents, bipolar transistors have recently found applications in merged CMOS-bipolar circuits [1]-[3], and a SOI CMOS-bipolar process has been demonstrated in strip-heater recrystallized silicon [4]. Bipolar transistors have also been fabricated in SOI layers created by ion implantation of a buried insulator [5], [6]. However, neither of these techniques is adaptable to three-dimensional integration [7]. In order to explore the possibilities of bipolar transistors in three-dimensional (3-D) structures, we have fabricated vertical bipolar transistors in laser-recrystallized polysilicon films.

The electron minority-carrier diffusion length in  $10^{17}$  cm<sup>-3</sup> p-type laser-recrystallized polysilicon after a forming gas anneal has been measured in this laboratory to be roughly 4  $\mu$ m. Thus, according to elementary bipolar transistor theory, for a transistor with a base width of 0.2  $\mu$ m, base transport would "limit" the current gain to 750. Hence, high-performance bipolar transistors in laser-recrystallized polysilicon would not be limited by the minority-carrier diffusion length.

### II. FABRICATION

The transistors were fabricated in 0.75- $\mu$ m-thick laser-recrystallized polysilicon films on 1500 Å of thermal oxide. The films were implanted with phosphorus before recrystallization so that a uniform n-type doping of  $10^{17}$  cm<sup>-3</sup> resulted after the laser processing. This was chosen as

Manuscript received April 22, 1985; revised May 23, 1985. This work was supported by DARPA under Contract ONR-N00014-84-K007.

The authors are with Stanford Electronics Laboratories, Stanford University, Stanford, CA 94305.

a compromise between breakdown voltage and collector series resistance. The recrystallization was performed with an oxide cap and a scanning argon-ion laser with the beam shaped to an elliptical spot of roughly 200  $\mu m \times 15~\mu m$ , resulting in a thermal gradient similar to that described by Stultz [8]. The laser scan rate was 10–20 cm/s and substrates were held at 350°C. The beam power was approximately 15 W and adjacent scans were overlapped by 40 percent. A Secco etch [9] determined that the recrystallized films had a typical grain size of 50  $\mu m \times 200~\mu m$  and had a low-angle grain boundary (subgrain boundary) spacing within each grain of a few micrometers. These defects extended vertically through the films and ran parallel to the thermal gradient from the shaped laser beam.

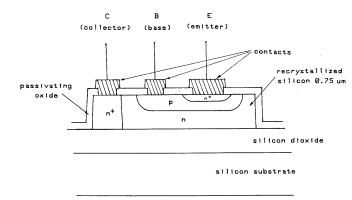

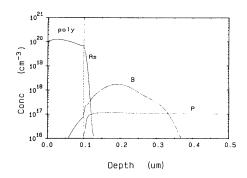

Conventional processing was then carried out to achieve the structure in Fig. 1. The n<sup>+</sup>collector contact regions were diffused before the base and emitter regions were created. Initial experiments with an implanted emitter and a base-emitter metallurgical junction depth of only 1000 Å indicated excessive hole recombination at the metal emitter contact, so a polysilicon emitter process was used [10], [11]. The chemical oxide resulting from the wafer cleaning was not etched off before the polysilicon deposition. After a base implant and anneal, 1000 Å of polysilicon was deposited and implanted with 50-keV As<sup>+</sup> at a dose of 1 × 10<sup>15</sup> cm<sup>-2</sup>. This was annealed at 600°C for 1 h and then 1000°C for 3 min, but due to the thermal mass of the furnace boat only 1 min at 1000°C was estimated. A doping profile calculated by SUPREM-III is shown in Fig. 2.

# III. RESULTS

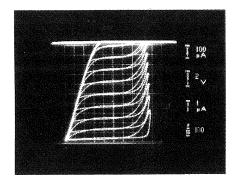

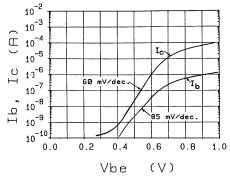

Extensive measurements by direct probing of the silicon prior to metallization were then performed on devices with  $20 \mu m \times 20 \mu m$  emitters. Initial common-emitter current gains of about 10 were measured on a curve-tracer, but they increased to near 40 after a 450°C forming gas anneal. A subsequent Ar:H (99:1) plasma anneal (still before metallization) at 350°C for 15 min further improved the gains to rougly 100 (Fig. 3). Gummel plots revealed that the forming gas and plasma anneals did not change the collector current (which had the ideal 60-mV/decade characteristic), but that the increases in gain were due to decreases in the base current. Even after the plasma anneal, a Gummel plot (Fig. 4) shows a nonideal base characteristic of 85-mV/decade. Control transistors with identical doping profiles fabricated simultaneously in n-type single-crystal silicon substrates had a gain of roughly 300 that was independent of the anneals and

Fig. 1. Cross section of vertical bipolar SOI transistors.

Fig. 2. Calculated doping profile of the polysilicon emitter transistors.

Fig. 3. Curve-tracer common-emitter characteristics of an SOI transistor after an Ar:H plasma anneal. The substrate-emitter voltage was -5 V.

Fig. 4. Gummel plot of an SOI transistor after an Ar:H anneal. The collector-base voltage was 0.0 V and the substrate-base voltage was 0.0 V.

displayed 60-mV/decade characteristics for both the base and collector currents. Since recrystallized devices with an emitter size of 200  $\mu m \times 200~\mu m$  (giving a larger area/perimeter ratio) actually had a lower gain, a dominant perimeter parasitic component of base current in the smaller transistors is unlikely. Thus, the 85-mV/decade base current in Fig. 4 indicates that the dominant source of base current (and limit on gain) is recombination in the base-emitter space-charge region.

The decrease in base currents caused by the forming gas and plasma anneals is probably due to hydrogen passivation of defects in the laser-recrystallized material and the corresponding decrease in the recombination rate. Efforts to further reduce the base current with more Ar:H plasma annealing actually sputtered away the emitter entirely so that metallization was not possible. A second wafer lot processed identically and metallized without any plasma anneal exhibited gains of 20-40 after a forming gas anneal.

A comparison of Gummel plots for the single-crystal and recrystallized transistors shows identical collector currents. This indicates that the minority-carrier diffusion coefficient (and hence mobility) of the electrons in the base is the same in laser-recrystallized and single-crystal silicon. Since the subgrain boundaries extend vertically through the film, this minority-carrier transport does not involve crossing subgrain boundaries. Majority-carrier mobility measurements in recrystallized films with no grain boundaries have shown similar agreement with bulk single-crystal values [12].

Since the subgrain boundary spacing was only a few micrometers and the emitter size was  $20~\mu m \times 20~\mu m$ , all devices contained these vertical defect structures, and many probably contained grain boundaries as well. However, no yield loss from collector-emitter shorts due to subgrain boundary or grain boundary diffusion of the emitter dopant was observed for the  $1000\,^{\circ}\text{C}$  drive-in, although for higher drive-in temperatures ( $1050~\text{or}~1100\,^{\circ}\text{C}$ ) many such shorts were seen. Grain and subgrain boundaries can be eliminated by using seeding techniques [13].

The transistors exhibited a considerable ( $\sim 5\text{-k}\Omega$ ) series resistance which increased with a negative substrate bias. This can be explained by the resistance of the thin, lightly doped collector layer under the base. This layer can be depleted by the collector-base bias and by substrate gating effects. Further experiments to create a heavily doped n<sup>+</sup> region on the bottom of the recrystallized film are in progress.

# IV. CONCLUSION

High-performance vertical bipolar transistors are indeed possible in laser-recrystallized polysilicon films, and base-emitter space-charge region recombination is the limit on the current gain. The nonideal base current characteristics in laser-recrystallized films may preclude low-current applications, but a gain of 100 at higher currents is more than adequate for current-driver or logic applications. Since laser recrystallization is suitable for three-dimensional structures, 3-D bipolar devices should be possible.

#### **ACKNOWLEDGMENT**

The authors would like to thank G. Bronner for providing the mask set. Special thanks go to Y. Kwark and other members of the Swanson group for their helpful discussions.

## REFERENCES

- [1] O. Minato, T. Masuhara, T. Sasaki, Y. Sakai, and T. Hayashida, "A HI-CMOSII 8K × 8b static RAM," in ISSCC Dig. Tech. Pap., 1982, pp. 256-257.

- [2] J. Miyamoto, S. Saitoh, H. Momose, H. Shibata, K. Kanzaki, and S. Kohyama, "A 1.0 μm n-well CMOS/bipolar technology for VLSI circuits," in *IEDM Tech. Dig.*, 1983, pp. 63-66.

- [3] E. L. Hudson and S. L. Smith, "An ECL compatible 4K CMOS RAM," in ISSCC Dig. Tech. Pap., 1982, pp. 248-249.

- [4] B-Y. Tsaur, R. W. Mountain, C. K. Chen, and J. C. C. Fan, "Merged CMOS/bipolar technologies utilizing zone-melting recrystallized SOI films," *IEEE Electron Device Lett.*, vol. EDL-5, pp. 461-463, 1984.

- [5] E. W. Greeneich and R. H. Reuss, "Vertical n-p-n bipolar transistors fabricated on buried oxide SOI," *IEEE Electron Device Lett.*, vol.

- EDL-5, pp. 91-93, 1984.

- [6] H. Münzel, G. Albert, and H. Strack, "Vertical bipolar transistors on buried silicon nitride layers," *IEEE Electron Device Lett.*, vol. EDL-5, pp. 283-285, 1984.

- [7] M. Nakano, "3-D SOI/CMOS," IEDM Tech. Dig., 1984, pp. 792-795.

- [8] T. J. Stultz and J. F. Gibbons, "The use of beam shaping to achieve large-grain cw laser-recrystallized polysilicon on amorphorous substrates," Appl. Phys. Lett., vol. 39, pp. 498-500, 1981.

- F. Secco d'Aragona, "Dislocation etch for (100) planes in silicon,"

J. Electrochem. Soc., vol. 119, pp. 948-951, 1972.

- [10] J. Graul, A. Glasl, and H. Murrman, "High-performance transistors with arsenic-implanted polysil emitters," *IEEE J. Solid-State Circuits*, vol. SC-11, pp. 491-495, 1976.

- [11] H. C. deGraaff and J. G. deGroot, "The SIS tunnel emitter: A theory for emitters with thin interface layers," *IEEE Trans. Electron Devices*, vol. ED-26, pp. 1771-1776, 1979.

- [12] T. J. Stultz, J. C. Sturm, and J. F. Gibbons, "Beam processing of silicon with a scanning cw Hg lamp," in *Proc. Mater. Res. Soc. Symp.*, vol. 13, J. Narayan, W. L. Brown, and R. A. Lemons, Eds. New York: North-Holland, Nov., 1982, pp. 463-475.

- [13] H. W. Lam, R. F. Pinizzotto, and A. F. Tasch, Jr., "Single crystal silicon-on-oxide by a scanning cw laser induced lateral seeding process," J. Electrochem Soc., vol. 128, pp. 1981-1986, 1981.