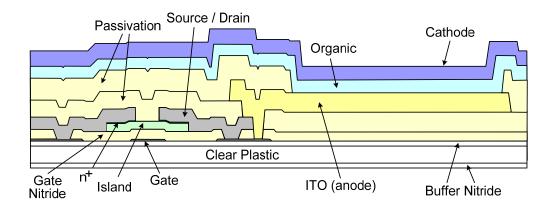

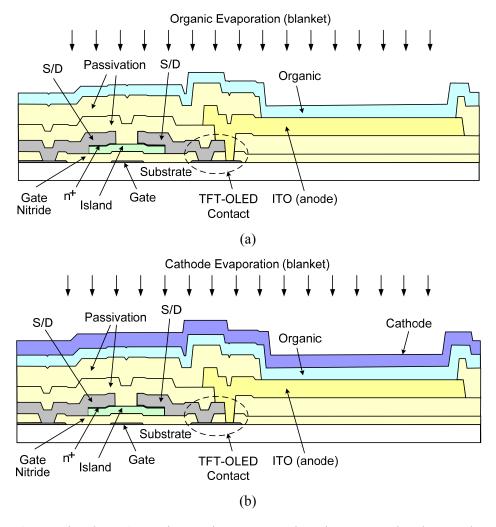

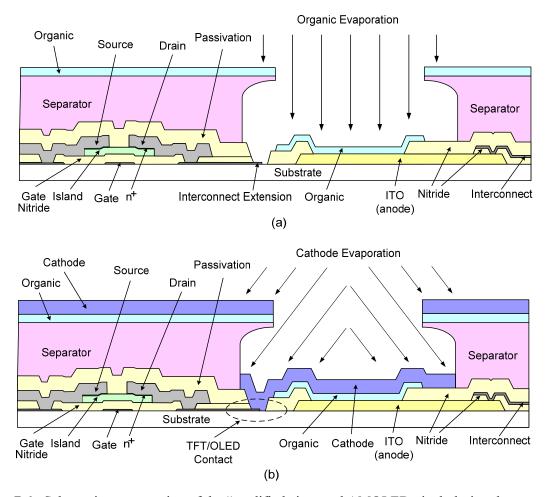

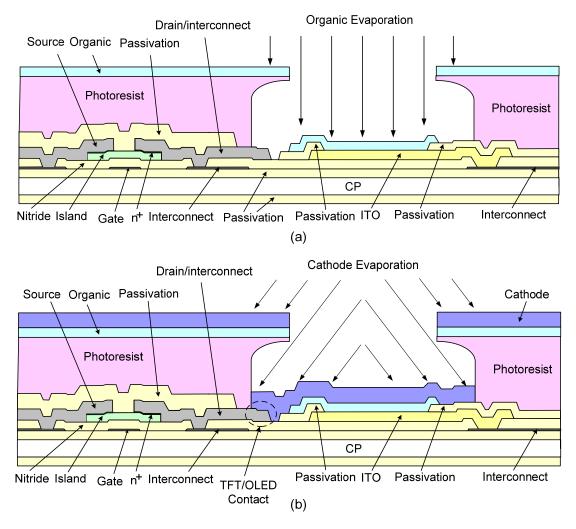

**Fig. 4.3.** Schematic cross-section of a 2-TFT AMOLED pixel fabricated in this work.

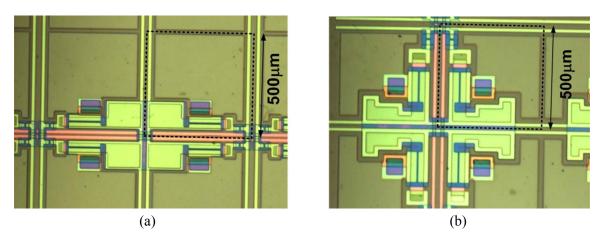

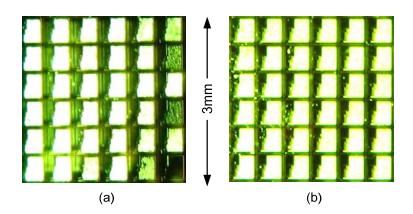

deposition has been optimized for best quality at 250°C for the 250°C and 285°C processes, and at 200°C for the 200°C process [12][13][14]. Dry etching is used next to pattern the a-Si:H islands and open contact vias to the bottom metal. The top metal (Cr/Al based) is then thermally evaporated and patterned by wet etching. The  $n^+$  a-Si:H is then cut at the backside of the a-Si:H channel by dry etching, and the samples are annealed at 180°C for 1 hour to repair the dry etching damage to the channel. The backplane is then passivated by a 250nm-thick layer of a-SiN<sub>x</sub>:H grown by PECVD at 125°C and dry-etching is used to open contact holes for ITO (OLED anode). Next, a 200nm-thick ITO layer is deposited at room temperature by DC-sputtering from an In<sub>2</sub>O<sub>3</sub>/SnO<sub>2</sub> target (with 90/10 weight ratio) in Ar/O<sub>2</sub> ambient and patterned by wet etching. A passivation layer is then deposited and patterned to cover the edges of ITO to avoid shorts between ITO and cathode in the OLED (evaporated subsequently). Dry etching is used next to open vias to the external pads in the passivation (not shown in the cross-section). Finally, the AMOLED structure is completed by the evaporation of small molecule green OLEDs through a pair of shadow masks for organic layers and cathode. The optical images of the arrays with 10µm and 20µm alignment tolerance prior to OLED evaporation are shown in Fig. 4.4 (a) and (b), respectively.

OLED evaporation was initially performed in Princeton University to develop the AMOLED fabrication process and conduct the primary characterization of the pixels. OLEDs used for this purpose were standard bi-layer small-molecule OLEDs with TPD (N,N'-Bis-(3-methylphenyl)-N,N'-diphenylbenzidine) hole transport layer (~3nm-thick) and Alq<sub>3</sub> (aluminum tris-(8-hydroxyquinoline)) electron transport/emissive layer (~3nm-thick)

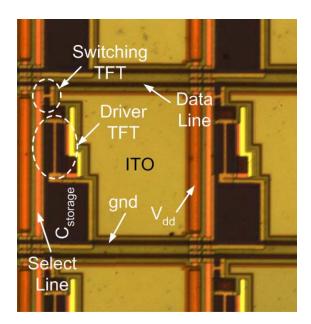

**Fig. 4.4.** Optical micrographs of the arrays with (a) 10μm and (b) 20μm alignment tolerance prior to OLED evaporation. The dashed lines show the pixel boundaries.

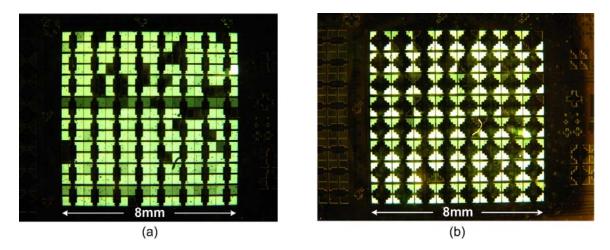

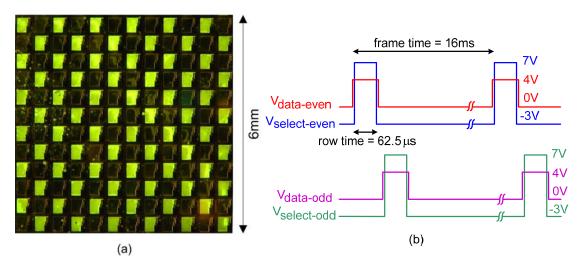

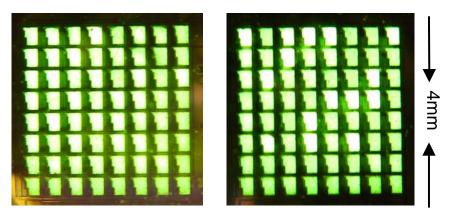

**Fig. 4.5.** Optical images of  $16\times16$  AMOLED test arrays fabricated with (a)  $10\mu$ m and (b)  $20\mu$ m alignment tolerance on clear plastic using a TFT backplane process temperature of 250°C.

thick). Indium-tin-oxide (ITO) was used as the OLED anode (~80nm-thick) and Mg/Ag with 1/10 ratio (~10nm-thick) followed by 100nm-thick Ag layer as the cathode. After AMOLED process development with standard OLEDs, a high quality green phosphorescent OLED (PHOLED <sup>TM</sup>) [15][16] was used instead. The PHOLEDs were deposited at Universal Display Corporation (UDC) in collaboration with Dr. Kamala Rajan and Dr. Michael Hack.

**Stress Engineering** – Controlling the mechanical stress in the deposited layers is crucial in order to obtain a flat surface with crack-free layers, especially at high process temperatures (250°C and 285°C) where the dimensional change in the substrate becomes significant (even with the low coefficient of thermal expansion of the clear plastic

substrates). The mechanical stress in the PECVD-grown layers can be adjusted by the plasma power density as established by our group [17][18]. The buffer nitride layers on both sides of clear plastic are grown at a plasma power density of 200mW/cm² resulting in tensile films balancing out the stress levels in each other and laying out the passivated substrate flat. Both bottom and top metal layers are tri-layers of Cr/Al/Cr with thin and thus low-tensile-stress Cr layers (15nm) for adhesion and low-stress Al layers for sufficient conduction. The gate nitride and *a*-Si:H are deposited at plasma power densities of 22mW/cm² and 17mW/cm² respectively, resulting in compressive films. The n<sup>+</sup> *a*-Si:H layer grown at 17mW/cm² is tensile, similar to the top and bottom Cr layers, and balances out the stress from the compressive layers. The nitride passivation layer on the device side and the sputtered ITO are nearly stress-free. The overall result is a crack-free backplane with a flat surface, ready for OLED evaporation.

## 4.4 Experimental Results

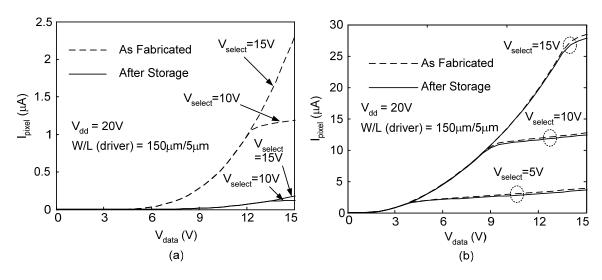

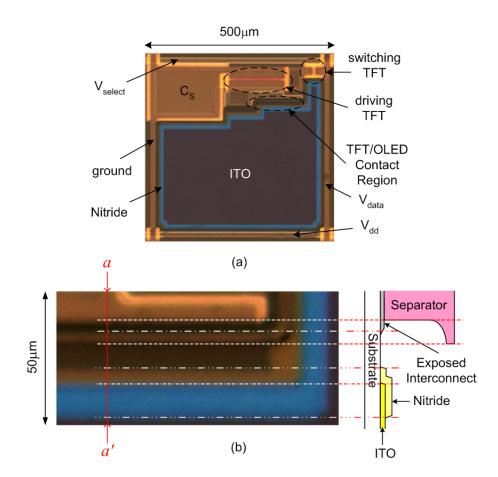

The optical images of the 16×16 AMOLED test arrays fabricated with 10μm and 20μm alignment tolerance are shown in Fig. 4.5 (a) and (b), respectively. The TFT backplane process temperature for these arrays is 250°C. The process yields for the test arrays with 10μm and 20μm alignment tolerance shown here are about 75% and 85%, respectively. However, we found no overall correlation between the alignment tolerance and process yield for the two alignment tolerances tried experimentally. The yield loss does not reflect a fundamental issue and is mainly related to the typical limitations of laboratory scale processing equipment and environment. The inset in Fig. 4.8 shows a process yield of about 96% for an 8×8 AMOLED test array. We have characterized the AMOLED test arrays by measuring the DC and AC characteristics, as well as the reliability of light emission over time.

#### 4.4.1 Pixel Characteristics

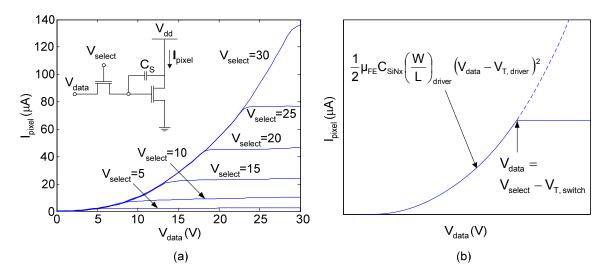

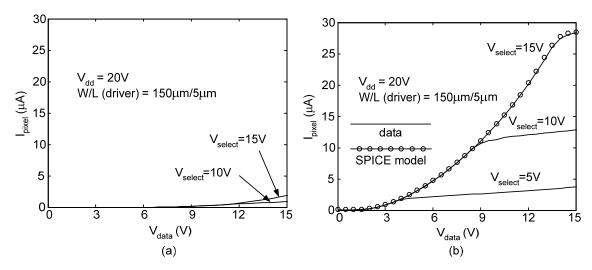

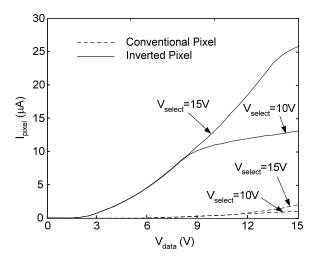

The pixel characteristics were investigated both prior and after the OLED evaporation. The backplane pixel was characterized by grounding the source of the driver TFT and measuring the pixel current while sweeping the data voltage at various select voltages (Fig. 4.6 (a)). The overlapping part of the curves shows the output characteristics of

**Fig. 4.6.** (a) The DC output characteristics of the 2-TFT pixel backplane (prior to OLED evaporation) with the source of the driver TFT grounded as shown in the inset, and (b) the illustration of the ideal output characteristics of the 2-TFT pixel assuming the switching TFT is an ideal switch with no subthreshold as explained in the text.

driver TFT in saturation, while the non-overlapping parts reflect the subthreshold characteristics of the switching TFT. This can be most simply explained by assuming that the switching TFT is an ideal switch, i.e. if  $V_{GS, \, switch} > V_{T, \, switch}$  the switching TFT is in the ON state, and if  $V_{GS, \, switch} < V_{T, \, switch}$  it is in the OFF state (Fig. 4.6 (b)). Therefore if  $V_{data} < V_{select} - V_{T, \, switch}$  the switching TFT is ON and the data voltage is transferred to the gate

Fig. 4.7. AMOLED pixel QVGA leakage test prior to OLED evaporation with a  $1M\Omega$  resistor to simulate the OLED. The voltage drop across the resistor during a frame time is negligible confirming efficient charge storage.

**Fig. 4.8.** DC output characteristics of an AMOLED pixel fabricated on clear plastic. The inset shows an image of an 8×8 AMOLED test array fabricated on clear plastic at 250°C.

of the driver TFT, i.e.  $V_{GS,\ driver} = V_{data}$ . But if  $V_{data} \ge V_{select} - V_{T,\ switch}$  the switching TFT remains in the ON/OFF transition state and  $V_{GS,\ driver} = V_{select} - V_{T,\ switch}$ . In practice, the switching TFT is not an ideal switch and therefore in the latter case it operates in the subthreshold mode. As a result, the gate voltage of the driver TFT increases slightly with increasing the data voltage as seen in the experimental data.

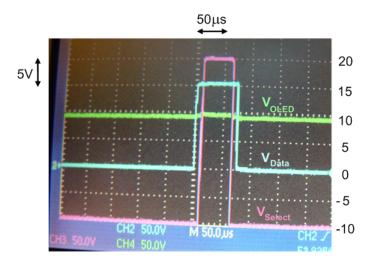

The backplane pixels were also tested with the QVGA signals to evaluate their charge storage capability. A  $1M\Omega$  resistor was used to simulate the OLED. Negligible

**Fig. 4.9.** QVGA timing of the pixel showing that the pixel brightness follows the program voltage on the data line, consistent with the DC output characteristics.

voltage drop on the resistor during a frame time indicates a low leakage current (primarily the off-current of the switching TFT) and efficient charge storage (Fig. 4.7).

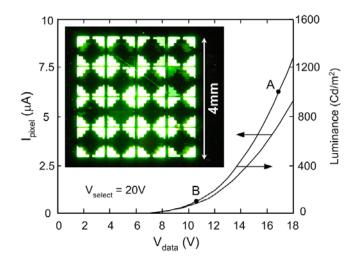

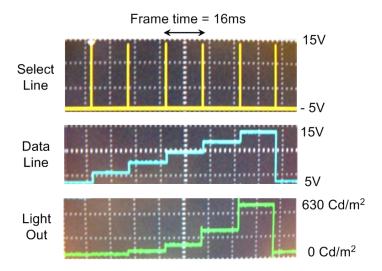

The DC output characteristics of a finished AMOLED pixel are given in Fig. 4.8. A luminance intensity of 1000Cd/m<sup>2</sup> is obtained at a data voltage of 16.8V and corresponds to an OLED efficiency of 57Cd/A. The QVGA timing of the pixels shows sufficient voltage storage over the frame time (Fig. 4.9).

# 4.4.2 Electrical Reliability

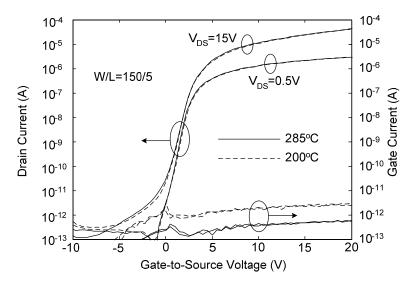

The DC output characteristics of typical driving TFTs fabricated on clear plastic at 200°C and 285°C are plotted in Fig. 4.10. It is observed that the on-state drive current is not essentially affected by changing the process temperature. Both TFTs show an apparent (i.e. not corrected for contact resistance) effective mobility of  $0.63 \text{cm}^2/\text{Vs}$  and an apparent threshold voltage of 2.1V in the saturation regime. However, the lower gate leakage current for the 285°C process shows improvement in the quality of gate nitride at higher process temperatures. It should be noted that there are statistical variations in the mobilities and threshold voltages of the measured TFTs on all samples (Chapter 5). The two TFT characteristics plotted in Fig. 4.10 were intentionally chosen to have very close threshold voltages and mobilities to show that the on-state TFT characteristics are not particularly correlated with the process temperature provided that the growth conditions

**Fig. 4.10.** DC output characteristics of the driver TFTs fabricated on clear plastic at 200°C and 285°C process temperatures.

for the TFT stack are optimized for each deposition condition.

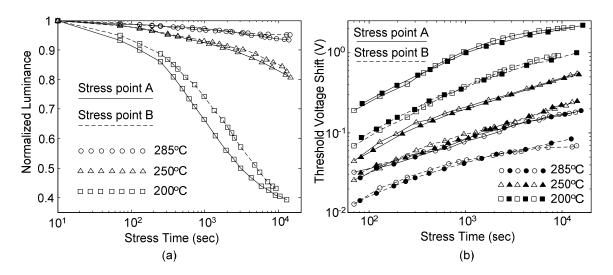

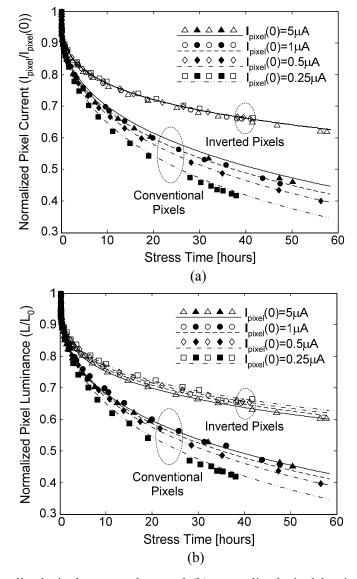

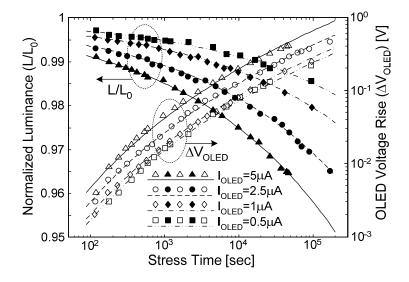

The process temperature drastically affects the stability of AMOLED pixels. Each pixel was stressed at two different pixel currents corresponding to pixel luminance intensities of 1000Cd/m² and 100Cd/m² (points A and B marked on the luminance curve in Fig. 4.8). For each stress point, the bias voltages on the select line (20V) and data line (with values corresponding to the initial pixel luminance at points A and B) were kept constant and the pixel luminance was measured versus time. Fig. 4.11 (a) shows the luminance drop under the mentioned stress conditions for pixels processed at three process temperatures, 200°C, 250°C and 285°C. The luminance intensities are normalized to their initial values (100Cd/m² for stress point B and 1000Cd/m² for stress point A). In all curves, the pixel luminance drops over time. It is observed that for each process temperature, the luminance degradation is faster at stress point A than at stress point B, and more importantly degradation proceeds significantly faster at lower TFT process temperatures. Since the temperature is the only process variable, faster luminance degradation at lower TFT process temperatures may be attributed to a faster threshold voltage increase in the driver TFT, which reduces the pixel current accordingly. Note that

**Fig. 4.11.** (a) Luminance as a function of DC stress time for the AMOLED pixels fabricated at three process temperatures on clear plastic. The Stress points A and B correspond to the points marked on the luminance curve in Fig. 4.8 and (b) threshold voltage shift of the driver TFT as a function of DC stress time extracted from luminance data of part (a) assuming negligible OLED luminance degradation (empty symbols) and measured threshold voltage shift of individual test driver TFTs under the same DC bias stress (full symbols).

on this time scale, the effect of OLED luminance degradation is negligible due to the relatively long lifetime of the green phosphorescent OLED [15][16]. The faster drop at stress point A comparing to stress point B may be explained by the increased charge trapping in the gate nitride and defect creation in *a*-Si:H at higher gate voltages, resulting in a larger threshold voltage shift in the driving TFT. As observed in Fig. 4.11(a), the improvement in the pixel reliability at higher process temperatures is significant. After 4 hours of continuous stress, the pixel brightness drops to about 40% of its initial value for the 200°C process, while for the 285°C process the brightness drops to only about 95%. This result demonstrates the impact of increasing the process temperature on improving the reliability of AMOLED pixels. Such high process temperatures are not conventionally possible because of the thermal constraints of clear plastic substrates which limit the TFT process to low temperatures. Therefore new clear plastic substrates with thermal properties that allow processing at such high temperatures are essential to flexible bottom-emitting AMOLED displays based on *a*-Si:H.

To confirm that the luminance degradation of the fabricated AMOLED pixels is mainly due to the *a*-Si:H TFT threshold voltage shift, we compare the threshold voltage shift of the driver TFTs calculated from the AMOLED luminance data of Fig. 4.11(a) assuming no OLED degradation, with the directly measured threshold voltage shift of individual test driver TFTs under the same DC bias stress, in Fig. 4.11(b). The small differences between these data verify that the pixel luminance degradation is mainly a result of the threshold voltage shift of the driver TFTs.

Although the improvement achieved in AMOLED reliability by increasing the process temperature is significant, it is still not sufficient for commercial display products. The stability requirement of *a*-Si:H TFTs for driving OLEDs and improving the lifetime of *a*-Si:H TFTs to meet this requirement is presented in Chapter 5.

#### 4.5 Summary and Conclusion

The design and fabrication of AMOLED pixel arrays on high-temperature flexible clear plastic substrates at temperatures close to 300°C was presented in this chapter. The process temperature of nearly 300°C is an improvement of about 150°C compared to previous demonstrations. The electrical stability measurements of the pixels show the

impact of high temperature processing on improving the pixel reliability. Controlling the mechanical stress of the deposited layers and adhesion of the layers was essential to the development of the plastic-compatible process by ensuring crack-free layers and a flat backplane prior to OLED evaporation.

## References:

- [1] H. Gleskova, S. Wagner, Z. Suo, "a-Si:H TFTs Made on Polyimide Foil by PECVD at 150°C", *Materials Research Society Symposium Proceedings*, vol. 508, pp. 73-78, April 1998

- [2] A. Constant, S.G. Burns, H. Shanks, C. Gruber, A. Landin, D. Schmidt, C. Thielen, F. Olympie, T. Schumacher, and J. Cobbs, "Development of thin film transistor based circuits on flexible polyimide substrates," *Proceedings of the Second International Symposium on Thin Film Transistor Technologies*, pp. 392-400, October 1995

- [3] E. Bonderover, S. Wagner and Z. Suo, "Amorphous silicon thin film transistors on Kapton fibers", *Materials Research Society Symposium Proceedings*, vol. 736, pp. 109-114, December 2002

- [4] H. Gleskova, and S. Wagner, "DC-gate-bias stressing of a-Si:H TFTs fabricated at 150°C on polyimide foil", *IEEE Transactions on Electron Devices*, vol. 48, no. 8, pp. 1667-1671, August 2001

- [5] Ke Long, "Towards Flexible Full-Color Active Matrix Organic Light-Emitting Displays: Dry Dye Printing for OLED Integration and 280oC Amorphous-Silicon Thin-Film Transistors on Clear Plastic Substrates", Ph.D. Dissertation: Princeton University, March 2006

- [6] K. R. Sarma, C. Chanley, S. Dodd, J. Roush, J. Schmidt, G. Srdanov, M. Stevenson, R. Wessel, J. Innocenzo, G. Yu, M. O'Regan, W. A. MacDonald, R. Eveson, K. Long, H. Gleskova, S. Wagner, and J. C. Sturm, "Active Matrix OLED Using 150°C a-Si TFT Backplane Built on Flexible Plastic Substrate", *Proceedings of the Annual Laser and Electro-Optics Society (LEOS) Meeting*, vol. 5080, pp. 180-191, April 2003

- [7] J. H. Ahn, E. Y. Lee, S. H. Won, S. H. Han, S. M. Cho, J. H. Kim, T. J. Park, S. K. Kwon, Y. K. Lee, K. M. Kim, and J. Jang, "2 Inch AMOLED with a-Si:H TFT using PVP Gate Insulator on Plastic Substrate", *SID Techical Digest*, vol. 36, no. 1, pp. 1542-1545, May 2005

- [8] Kunigunde H. Cherenack, "Fabricating Silicon Thin-Film Transistors on Plastic at 300°C", Ph.D. Dissertation: Princeton University, December 2009

- [9] H. Yi, R. Hattori and J. Kanicki, "Improved *a*-Si:H TFT pixel electrode circuits for active-matrix organic light emitting displays", *IEEE Transactions on Electron Devices*, vol. 48, no. 7, pp. 1322-1325, July 2001

- [10] A. Nathan, A. Kumar, K. Sakariya, P. Servati, K. S. Karim, D. Striakhilev and A. Sazonov, "Amorphous silicon back-plane electronics for OLED displays", *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 10, no. 1, pp. 58-69, January-February 2004

- [11] K. Cherenack, B. Hekmatshoar, S. Wagner, J. C. Sturm, "Self-alignment techniques for fabricating a-Si TFTs at 300°C on clear plastic", *The Proceedings of the 5th International TFT Conference*, paper 9.5, March 2009

- [12] K. Long, A. Kattamis; I-C. Cheng, H. Gleskova, S. Wagner and J.C. Sturm, M. Stevenson, G. Yu and M O'Regan, "Active-Matrix Amorphous-Silicon TFTs Arrays at 180°C on Clear Plastic and Glass Substrates for Organic Light-Emitting Displays", *IEEE Transactions on Electron Devices*, vol. 53, no. 8, pp. 1789-1796, August 2006

- [13] K. Long, A. Kattamis, I-C. Cheng, H. Gleskova, S. Wagner and J.C. Sturm, "Increased reliability of a-Si TFT's deposited on clear plastic substrates at high temperatures", *Device Research Conference, Conference Digest*, vol. 1, pp. 141-142, June 2005

- [14] K. Long, A. Kattamis, I-C. Cheng, H. Gleskova, S. Wagner and J.C. Sturm, "Stability of amorphous-silicon TFTs deposited on clear plastic substrates at 250°C to 280°C", *IEEE Electron Device Letters*, vol. 27, no. 2, pp. 111-113, February 2006

- [15] M. S. Weaver, R. C. Kwong, V. A. Adamovich, M. Hack and J. J. Brown, "Recent Advances in phosphorescent OLEDs for small- and large-area-display sizes", *Journal of the Society for Information Display*, vol. 14, no. 5, pp. 449-452, May 2006

- [16] B. W. D'Andrade, "White PHOLED for Lighting", *Proceedings of the Annual Laser and Electro-Optics Society (LEOS) Meeting*, pp. 59-60, October 2007

- [17] I-C. Cheng, A. Kattamis, K. Long, J. C. Sturm, and S. Wagner, "Stress control for overlay registration in a-Si:H TFTs on flexible organic-polymer-foil substrates", *Journal of the Society for Information Display*, vol. 13, no. 7, pp. 563-568, July 2005

- [18] K. Long, I-C. Cheng, A. Kattamis, H. Gleskova, S. Wagner, and J. C. Sturm, "Amorphous-silicon thin-film transistors made at 280°C on clear-plastic substrates by interfacial stress engineering", *Journal of the Society for Information Display*, vol. 15, no. 3, pp. 167-176, March 2007

# **High Lifetime** *a***-Si:H TFTs for Active-Matrix OLED Displays**

As discussed in the previous chapter, increasing the process temperature improves the stability of *a*-Si:H TFTs significantly and enhances the reliability of light emission in AMOLED pixels. However, in the present chapter, it is shown that the improvement achieved in *a*-Si:H TFT lifetime by increasing the process temperature is not sufficient and further improvement in lifetime is necessary for sufficient AMOLED reliability. Also in this chapter, the mechanisms responsible for the degradation of lifetime in *a*-Si:H TFTs are discussed and it is demonstrated that the lifetime of *a*-Si:H TFTs can be significantly enhanced by improving the quality of the gate nitride and the quality of *a*-Si:H close to the *a*-Si:H/nitride interface. Comparison with the literature shows that at low gate electric fields required for driving high-efficiency OLEDs, the lifetimes of the improved *a*-Si:H TFTs developed in this work are far in excess of the lifetimes of the *a*-Si:H TFTs reported by other groups.

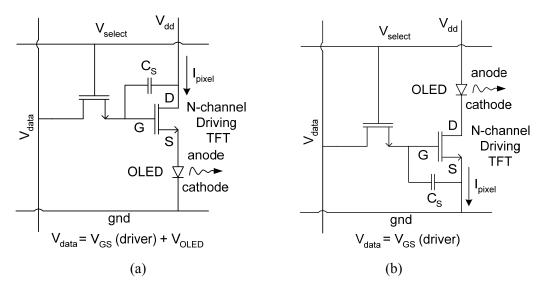

## 5.1 Lifetime Requirements for Driving OLEDs

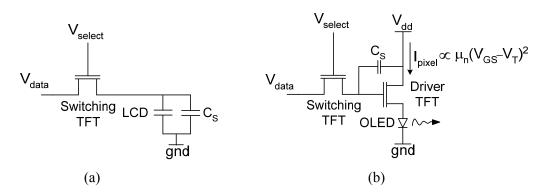

Standard *a*-Si:H TFTs are in widespread production for manufacturing the backplane for active-matrix liquid crystal displays (AMLCDs). However, driving OLEDs is far more demanding than driving LCDs. This is because in AMLCDs (Fig. 5.1(a)), the LCD is a capacitive load, and the TFT just acts as a digital switch. This makes the circuit fairly insensitive to changes in the TFT threshold voltage. Further, the duty cycle of the TFT is as low as 0.1%, minimizing the time the TFT is in operation. However, in AMOLED pixels (Fig. 5.1 (b)), the OLED is driven in DC (i.e. 100% duty cycle) and the OLED current and thus brightness depends directly and continuously (in an analog fashion) on

Fig. 5.1. The schematic pixel circuit of (a) an AMLCD and (b) an AMOLED display.

the TFT drive current which is lowered by the TFT threshold voltage rise.

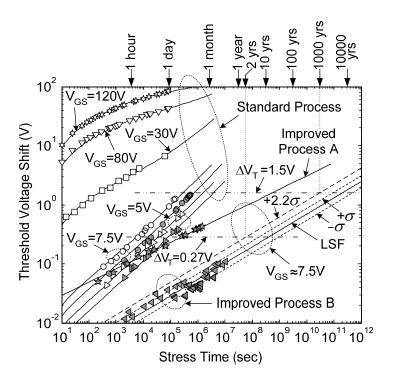

The sensitivity of the human eye to the changes in the pixel brightness and the resulting distortion of color balance are also very high. For commercial applications, the maximum allowable distortion of color balance occurs when the brightness of one of the primary colors (red, green or blue) drops 5% with respect to the others [1]. This allows a maximum drop of 5% in the TFT drive current. For drive conditions corresponding to  $1000\text{Cd/m}^2$  OLED brightness discussed in Chapter 4, this 5% drop corresponds to about 100mV shift in the TFT threshold voltage.

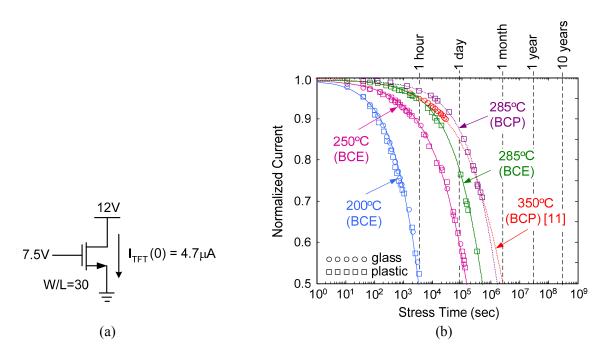

Fig. 5.2 shows the threshold shift of a standard a-Si:H TFT typical of that used in the AMLCD industry, which is made on glass at a process temperature of 350°C [5] (The gate nitride deposition temperature, the highest temperature step in the a-Si:H TFT process, and similar to the previous chapter, hereafter we will refer to it as the "process temperature"). Also shown are data for what were (before this thesis) what we best know to be the most stable a-Si:H TFTs fabricated on clear plastic substrates for various process temperatures, as will be needed for future display technologies [6][7]. Previous work by our group shows that the stability of a-Si:H TFTs depends on the TFT process conditions (including the process temperature) but it is not affected by the type of the substrate [6][7]. Therefore, the TFT stability requirement investigated in this section, applies to both glass and clear plastic substrates, as well as other types of substrates. As seen in Fig. 5.2, a 100 mV shift, corresponding to the 5% current drop described in the previous paragraph, occurs at only about 10 minutes for industry standard TFTs processed at temperatures and the best TFTs on plastic (processed at 300°C). This indicates that the threshold voltage stability of standard a-Si:H TFTs is not sufficient for driving OLEDs.

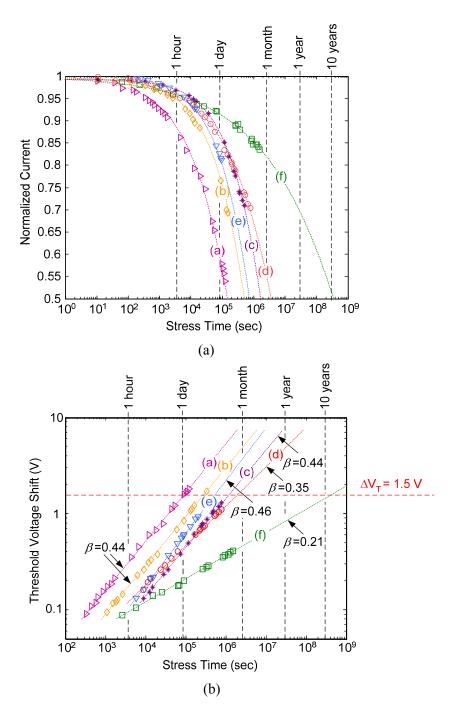

Since the AMOLED pixel brightness depends directly and continuously on the current of the driver TFT, from an application point of view, it is helpful to investigate the TFT lifetime by measuring the degradation of TFT drive current (biased in saturation) over time. Since the OLEDs are characterized by their luminance half-life, defined as the time the OLED luminance drops by 50% at constant DC current, similarly, we define the

**Fig. 5.2.** Threshold voltage shifts of *a*-Si:H TFTs processed at various temperatures on clear plastic [6][7] along with a reference TFT on glass [5]. The TFTs were stressed for 10 minutes at various gate electric fields.

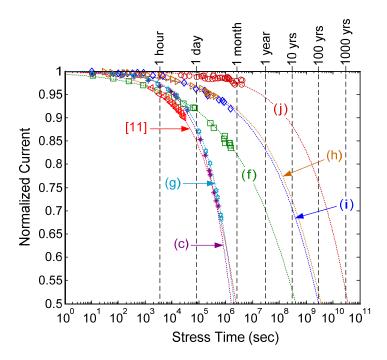

TFT current half-life as the time the TFT current drops to 50% under constant DC voltage bias in saturation. The extrapolated luminance half-life of high quality green phosphorescent OLEDs is as high as 30 years for an initial luminance of 1000Cd/m<sup>2</sup> [2]. Fig. 5.3 shows the degradation of the saturation current of standard *a*-Si:H TFTs over time at bias conditions required for driving OLEDs at a brightness of 1000Cd/m<sup>2</sup> (see Section 4.2) for various nitride deposition temperatures. As seen in the figure, the drive current half-lives of the TFTs are below 1 month, much shorter than the luminance half-life of the OLEDs. This indicates that the lifetime of standard *a*-Si:H TFTs is too short for driving OLEDs and therefore requires major improvement.

## 5.2 Threshold Voltage Shift Mechanisms

Improving the stability of a-Si:H TFTs requires knowledge of the TFT instability mechanisms. Conventionally, a-Si:H TFTs are stressed at high gate electric fields which are required for driving LCDs (typically larger than  $10^6$  V/cm). In addition, even for applications which require low gate electric fields such as driving OLEDs, stress measurements are conventionally performed at high gate electric fields to reduce the

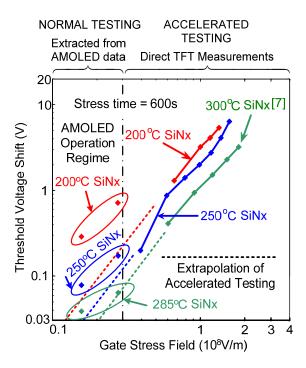

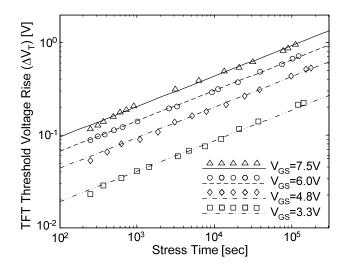

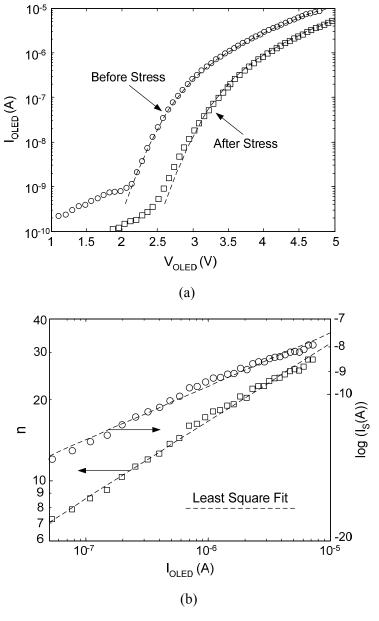

measurement time (typically referred to as "accelerated testing"). This is because the TFT threshold voltage shift is higher at higher gate electric fields, allowing shorter stress times for measuring the TFT threshold voltage shift. In Fig. 5.4, the threshold voltage shifts of the driver TFTs at  $1000\text{Cd/m}^2$  OLED drive conditions extracted from AMOLED luminance degradation data (see Fig. 4.11) corresponding to low gate electric fields (labeled as "normal testing") is compared against TFT threshold voltage shifts measured directly at high gate electric fields (labeled as "accelerated testing"). Interestingly, as seen in the figure, the TFT threshold voltage shift at high fields cannot be extrapolated back to low gate electric fields needed for driving OLEDs. This indicates that different mechanisms are responsible for the TFT instability at low and high gate electric fields.

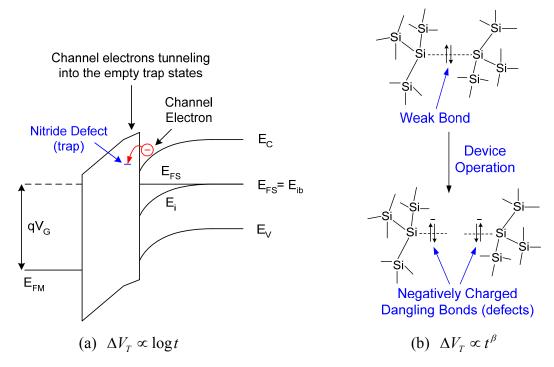

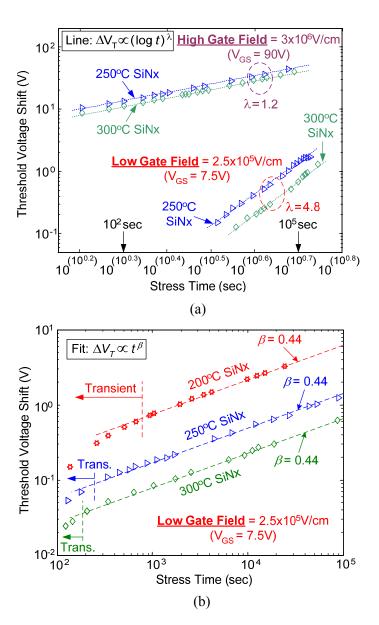

At high gate electric fields, the threshold voltage shift of a-Si:H TFTs is dominated by electron trapping in the gate nitride (Fig. 5.5 (a)), resulting in a logarithmic

**Fig. 5.3.** (a) TFT drive condition for  $1000\text{Cd/m}^2$  OLED brightness corresponding to a gate voltage bias of 7.5V for a TFT with 300nm-thick gate nitride (see Section 4.2) and (b) the degradation of *a*-Si:H TFT saturation current over time at this drive condition ( $V_{GS} = 7.5V$  and  $V_{DS} = 12V$ ) for various nitride deposition temperatures on glass and/or plastic. "BCE" and "BCP" refer to "back-channel etched" and "back-channel passivated" TFT structures, respectively (Section 3.1). The effect of the TFT structure on TFT lifetime is discussed in Section 5.3. The current drop from Ref. [11] was calculated from the published plot of threshold voltage shift vs. time which was measured at a gate bias stress of 8.0V, very close to our stress conditions.

time dependence of the TFT threshold voltage shift ( $\Delta V_T$ )

$$\Delta V_T \propto (\log t)^{\lambda} \tag{5.1}$$

where  $\lambda$  is a constant close to 1 [3][8][5][8]. At low gate electric fields, the creation of defects in *a*-Si:H and capturing of electrons by these defects (Fig. 5.5 (b)) is the dominant instability mechanism, and as discussed in Section 2.7, this instability mechanism results in a stretched exponential time dependence which can be approximated by a power law relation at short stress times

$$\Delta V_T \propto t^{\beta} \tag{5.2}$$

with values of  $\beta$  in the range of 0.2-0.6 reported in the literature [5][8][9][10].

As seen in Fig. 5.6 (a), a value of 1.2 for  $\lambda$  extracted from fitting our experimental high-field threshold voltage shift data to Eq. (5.1) is close to the theoretical value of 1, indicating the dominance of electron trapping in the gate nitride at high gate electric fields. However, as seen in Fig. 5.6 (b), at low gate electric fields, the rate of the TFT threshold voltage shift is faster than could be predicted by the charge trapping model, as indicated by an extracted values of 4.8 for  $\lambda$  which is much larger than the theoretical value of 1. In contrast, a value of 0.44 extracted for  $\beta$  by fitting the low field threshold voltage shift data to Eq. (5.2) indicates that defect creation in *a*-Si:H is the dominant instability mechanism at low gate electric fields.

It is interesting to note that the low-field threshold voltage shift has a strong dependence on the gate nitride deposition temperature (Fig. 5.6 (b)). This is counterintuitive, as the time dependence of the threshold voltage shift in this regime indicates the dominance of defect creation in the *a*-Si:H channel rather than charge trapping in the gate nitride. The dependence of low-field stability on the gate nitride indicates that the nitride quality affects the quality of *a*-Si:H close to the *a*-Si:H/nitride interface where defect formation in *a*-Si:H and then charge trapping occurs. As discussed in Section 3.2, since *a*-Si:H is deposited after the gate nitride, the quality and microstructure of *a*-Si:H can be affected by that of the nitride underneath it. Therefore, the quality of the gate nitride is important at both high and low gate electric fields. This will be further discussed in Section 5.4.

**Fig. 5.4.** Accelerated testing (direct TFT threshold voltage shift measurements and high gate electric fields) and normal testing (extraction of TFT threshold voltage shift from luminance drop in AMOLED pixel at normal drive conditions). Extrapolation of accelerated testing data underestimates the threshold voltage shift at low gate electric fields.

**Fig. 5.5.** Instability mechanisms responsible for threshold voltage shift in a-Si:H TFTs, (a) electron trapping in the gate nitride resulting in a logarithmic time dependence and (b) creation of defects in a-Si:H resulting in a power law relation at relatively short stress times.

# 5.3 Improving the a-Si:H Channel with Hydrogen Dilution

Since the low-field stability is dominated by the creation of defects in a-Si:H, improving the quality of a-Si:H is critical for improving the stability of a-Si:H TFTs. Our experiments show that this can be achieved by including hydrogen dilution in silane for growing the a-Si:H channel, both for a-Si:H TFTs on glass and plastic substrates.

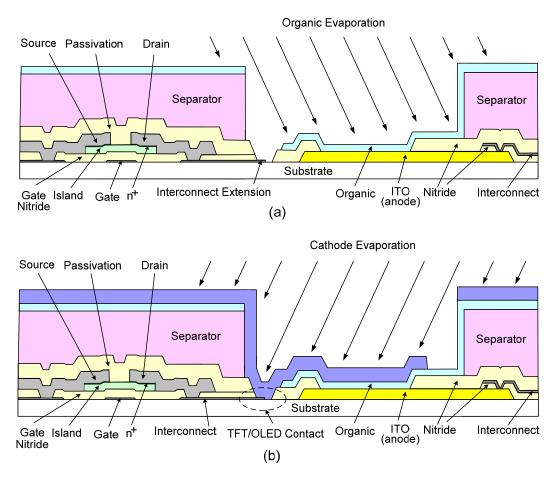

# **5.3.1** Experimental Structure

Inverted-staggered bottom-gate a-Si:H TFTs were fabricated with standard "back-channel etched" (BCE) or "back-channel passivated" (BCP) structures (Section 3.1) on clear plastic. Control samples were also prepared on glass substrates. In the back-channel etched structure, the  $n^+$  a-Si:H layer is deposited in a single run with the gate nitride and undoped a-Si:H and subsequently removed from the back-side (top) of the channel after the deposition and patterning of the source/drain metal. In the back-channel passivated structure, the back-channel passivation (nitride) is deposited in a single run with the gate nitride and undoped a-Si:H and the  $n^+$  a-Si:H layer is deposited after patterning the back-channel passivation which defines the channel length. The latter process seals the a-Si:H channel in situ with a nitride layer immediately after a-Si:H deposition at the cost of an extra mask step.

All TFTs were made with 300nm-thick gate nitride layers grown at a plasma power density of 22mW/cm<sup>2</sup> and a chamber pressure of 500mtorr. The 250-nm-thick *a*-Si:H layers were grown at a chamber pressure of 500 mtorr and at a plasma power density of 17 mW/cm<sup>2</sup>. The 30-nm-thick n<sup>+</sup> *a*-Si:H layers were grown at 250°C, at 17mW/cm<sup>2</sup> and 500mtorr. All *a*-Si:H TFTs were annealed at 180°C in vacuum for one hour to repair plasma etch damage. The process parameters which were varied are listed in Table 5.1.

# **5.3.2** Stress Conditions and Extraction of Threshold Voltage

For all our low-field stress measurements, the TFTs were biased in saturation (with a constant drain voltage of 12V) and the threshold voltage shift (Fig. 5.7(a)) was calculated from the measured drop in the saturation current (Fig. 5.7(b)) using the model of a MOSFET in saturation (see Section 3.2)

**Fig. 5.6.** High-field and low-field threshold voltage shifts of back-channel etched (BCE) a-Si:H TFTs fabricated with different gate nitride deposition temperatures. (a) Plotting the TFT threshold voltage shifts in a semi-logarithmic plot shows that the high-field threshold voltage shifts match the nitride charge trapping model ( $\lambda \approx 1$ ) while the low-field threshold voltage shift do not ( $\lambda \approx 1$ ). (b) Plotting the same low-field threshold voltage shifts in a logarithmic plot shows that the low-field threshold voltage shifts match the defect creation model in a-Si:H.

$$\Delta V_{T,sat} = (V_{GS} - V_{T0}) \left( 1 - \sqrt{I_{TFT,sat}(t) / I_{TFT,sat}(0)} \right)$$

(5.3)

where  $\Delta V_T$  is the threshold voltage shift,  $V_{GS}$  the gate-source voltage,  $V_{T0}$  the initial threshold voltage,  $I_{TFT}$  the TFT drain current and the subscript "sat" refers to the saturation regime.

The measured change in mobility was negligible as expected from previous work [9][10][11]. We also found that mobility changed little – in transistors which had a threshold voltage shift of ~1.2V (corresponding to a 50% drop in current for a gate voltage of ~ 7.5V, standard linear region measurements to separate threshold and mobility showed a mobility change of less than 1%. Saturation measurements were done for two reasons, (i) saturation is the realistic operating condition in AMOLED pixels, and (ii) changes in saturation current allow more accurate measurement of small the threshold voltage shifts than linear measurements and do not require stopping the stress to estimate the threshold voltage shift. A gate stress field of ~2.5×10<sup>5</sup> V/cm corresponds to a gate voltage of ~7.5V. Due to the statistical variation of the TFT threshold voltages (Table 5. 1) the gate stress voltages were slightly adjusted for each TFT measurement to assure the same  $V_{GS}$  – $V_T$  of ~5.3V and thus the same initial saturation current of ~30nA per micrometer gate width.

Stress experiments were typically done for a period of several weeks to give the data in Fig. 5.7 (a). The threshold voltage shifts versus time in Fig. 5.7(a) were then extrapolated with a straight line in a log-log plot based on Eq. (5.2) to predict the shift for longer times. These extrapolated threshold voltages were then used to predict current vs. time in Fig. 5.7 (b) using the model of a MOSFET in saturation

$$I_{TFT,sat}(t) = I_{TFT,sat}(0)[1 - \Delta V_{T,sat}(t)/(V_{GS} - V_{T0})]^{2}$$

(5.4)

| Sample/<br>Curve<br>Label | TFT Back<br>Channel | SiN <sub>x</sub><br>Temp.<br>(°C) | a-Si:H Deposition |                    |                                                       | A a a li a              | N.T L. : 124                      | (D) 1 1 1                |

|---------------------------|---------------------|-----------------------------------|-------------------|--------------------|-------------------------------------------------------|-------------------------|-----------------------------------|--------------------------|

|                           |                     |                                   | Temp.             | Pressure<br>(Torr) | [H <sub>2</sub> ] / [SiH <sub>4</sub> ]<br>Flow Ratio | Annealing<br>Temp. (°C) | Mobility<br>(cm <sup>2</sup> /Vs) | Threshold<br>voltage (V) |

| (a)                       | Etched              | 250                               | 250               | 0.5                | 0                                                     | 180                     | 0.63±0.06                         | 2.0±0.3                  |

| (b)                       | Etched              | 285                               | 250               | 0.5                | 0                                                     | 180                     | 0.63±0.04                         | 2.0±0.3                  |

| (c)                       | Passivated          | 285                               | 250               | 0.5                | 0                                                     | 180                     | 0.64±0.04                         | 2.3±0.1                  |

| (d)                       | Passivated          | 285                               | 250               | 0.5                | 0                                                     | 180+260                 | 0.62±0.05                         | 2.4±0.3                  |

| (e)                       | Passivated          | 285                               | 250               | 0.8                | 10                                                    | 180                     | 0.66±0.05                         | 2.2±0.1                  |

| (f)                       | Passivated          | 285                               | 250               | 0.8                | 10                                                    | 180+260                 | 0.61±0.04                         | 2.4±0.2                  |

**Table 5.1.** Properties and process conditions that were varied and the saturation mobility and threshold voltage of the fabricated TFTs (with standard deviations). The parameters that were held constant are described in the text. The W/L ratio is  $150 \mu m/5 \mu m$  for all the TFTs.

## 5.3.3 Effect of Hydrogen Dilution on TFT Stability

As discussed in 5.2, increasing the nitride deposition temperature improves the TFT stability at low fields by improving the quality of a-Si:H close to the a-Si:H/nitride interface. This improvement is observed in TFTs with gate nitride deposition temperature of 285°C (curve (b)) compared to TFTs with gate nitride deposition temperature of 250°C (curve (a)) which are included as a reference (both TFTs have "etched" structures). We now focus on comparing the TFTs with a fixed nitride deposition temperature of 285°C, i.e. curves (b) – (f). The TFTs with a-Si:H channel grown from pure silane and annealed at 180°C have a much lower threshold voltage shift in the "passivated" structure, curve (c), than in the "etched" structure, curve (b). An additional annealing of one hour in vacuum at 260°C slightly reduced threshold voltage shift in the "passivated" structure, curve (d), while this 260°C anneal degraded the DC characteristics of the "etched" TFTs so much that they were not measured further. This is consistent with the lasting damage created by plasma and process chemicals to the exposed back-channel. Varying the a-Si:H deposition temperature in the range of 230°C-280°C in both types of devices made no significant change. Hydrogen dilution slightly degraded the "passivated" devices, curve (e), compared to the "passivated" devices without hydrogen dilution, curve (c). The straight line fits to (a)-(e) have  $\beta$  in the range of 0.36-0.44 which is again consistent with defects in the a-Si:H close to the a-Si/nitride interface. Finally the 260°C anneal of the "passivated" sample (f) grown with hydrogen dilution dramatically reduces the threshold voltage shift, fitting a  $\beta$  of 0.20. Extrapolating the threshold voltage shift of this TFT gives ~1.2V after 10 years of continuous operation, curve (f), representing a 100-fold increase from the devices of curve (a). The TFT half-life of 10 years is now comparable with the OLED half-life of 30 years and indicates that the "improved" a-Si:H TFTs may qualify for driving OLEDs.

#### 5.3.4 Physical Effect of Hydrogen Dilution

The role of hydrogen dilution in improving the lifetime of *a*-Si:H TFTs may be illustrated by the model of Fig. 5.9. Hydrogen radicals in plasma etch the weak Si-Si bonds *in situ* (i.e. at the growth surface, during growth) resulting in a material with fewer weak bonds.

**Fig. 5.7.** (a) Normalized TFT drain currents and (b) TFT threshold voltage shifts vs. time measured in saturation ( $V_{DS} = 12V$ ) at a constant gate field of  $\sim 2.5 \times 10^5$  V/cm (symbols: data points, lines: extrapolations based on Eq. (5.1). The threshold voltage shift of 1.5V marked on plot (a) corresponds to approximately 50% drop in the TFT currents.

As explained in Section 2.7.2, the weak bonds in *a*-Si:H (weak or strained Si-Si bonds) have different energies. The bonds with lower energies convert to defects (by bond

breaking and capturing electrons) on a shorter time scale than those with higher energies. Therefore, reducing the density of weaker bonds (i.e. reducing the low-energy band tail of the density of weak bonds) reduces the rate of bond breaking during device operation and improves the device stability.

This concept that hydrogen radicals can remove weak Si-Si bonds during growth is well-known. Adding much more hydrogen than presented in this thesis can actually lead to the growth of "nanocrystalline" or "microcrystalline" silicon, in which nearly all amorphous silicon is removed [13][14][15][16]. Although carrier mobility is higher in the nano/microcrystalline Si TFTs compared to *a*-Si:H TFTs, these devices suffer from high off-current, high device-to-device threshold voltage variation compared to *a*-Si:H TFTs, and typically poor stability[17][18][19][20]. Our work is novel in that it uses hydrogen dilution to "improve" the *a*-Si:H channel, with a focus on reducing "weak bonds" to improve *a*-Si:H TFT stability, while avoiding nano/microcrystalline growth. Earlier groups have observed that low amounts of hydrogen dilution affect the plasma properties during *a*-Si:H growth with an affect on TFT stability, but no lifetimes in excess of ~1 month were observed [21][22].

## 5.3.5 Comparison with *a*-Si:H TFTs from the Literature

Nearly all of our measurements of TFT stability were done with the TFT operated continuously in saturation. In most other stability work in the literature, the TFT is operated with small drain voltages in the linear regime. Since defect creation in a-Si:H depends on the density of mobile channel electrons, for a fair comparison, the threshold voltage shifts measured by other groups at low gate electric fields can be scaled to our conditions by the ratio of the density of mobile channel electrons at our stress conditions in saturation ( $Q_{ch,PU}$ ) to that of their stress conditions with small drain voltages ( $Q_{ch}$ )

$$\Delta V_{T, scaled} = \Delta V_T \times \frac{Q_{ch, PU}}{Q_{ch}} = \Delta V_T \times \frac{(2/3)C_{ins, PU}(V_{GS, PU} - V_{T0, PU})}{C_{ins}(V_{GS} - V_{T0})}$$

(5.5)

where  $C_{ins}$  is the gate dielectric capacitance per unit area of the channel,  $V_{T0}$  is the initial threshold voltage and the subscript PU refers to our TFTs. The 2/3 coefficient in this equation accounts for conducting our measurements in the saturation regime where the

density of mobile channel electrons is lower than that in the linear regime (used by other groups) by a factor of 2/3.

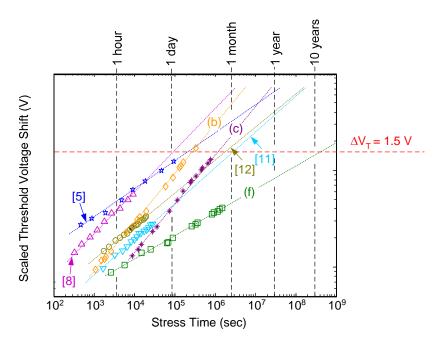

Fig. 5.10 compares the threshold shifts vs. time of *a*-Si:H TFTs compared to our work (curves (b), (c), and (f) repeated from Fig. 5.7 (b)). It is difficult to quantitatively compare the different sets of work because of different gate voltages and gate insulator thicknesses, meaning different electric fields in the gate insulator and different electron densities in the channel, both of which affect stability. However, all points are in the range where defect formation in *a*-Si:H is expected to dominate the shift in threshold. A visual comparison of the scaled threshold voltages (which physically means comparing the rate of electron trapping in the dangling bonds) shows clearly that the low-field stability of our improved *a*-Si:H TFTs with hydrogen dilution during *a*-Si:H deposition (curve (f)) is superior to that of standard *a*-Si:H TFTs reported in the literature (Fig. 5.10). In Chapter 6, we present a formal method for making a "fair comparison" of the stabilities of TFTs with different gate insulator materials and thicknesses measured under different gate voltages.

## 5.4 Improving the a-Si:H Channel by Improving the Gate Nitride

As discussed in Section 5.2, the quality of a-Si:H close to the a-Si:H/gate nitride interface can be improved by improving the quality of the gate nitride. In this section, we present experiments demonstrating that improving the quality of the gate nitride together with including hydrogen dilution for the growth of the a-Si:H channel can increase the TFT lifetime to over 1000 years. Improving the gate nitride quality has been pursued by

**Fig. 5.9.** Suggested mechanism for *in situ* removal of weak bonds by hydrogen radicals during *a*-Si:H growth. Silane is diluted with hydrogen during *a*-Si:H growth for this purpose.

**Fig. 5.10.**  $\Delta V_T$  vs. time (symbols: data points, lines: extrapolations) of the test TFTs (b), (c) and (f) (Table I) and the scaled  $\Delta V_T$  of *a*-Si:H TFTs reported in literature [5][8][11][12] based on Eq. (5.2). The TFT parameters are, Ref. 5: "etched" TFTs,  $V_{GS} = 20$ V,  $V_{T0} = 2.5$ V, insulator: SiN<sub>x</sub> 500nm, Ref. 7: "passivated" TFT's,  $V_{GS} = 25$ V,  $V_{T0} = 4.5$ V, insulator: SiO<sub>x</sub> 300nm+SiN<sub>x</sub> 50nm, Ref. 9: "passivated" TFTs,  $V_{GS} = 8$ V,  $V_{T0} = 1.3$ V, insulator: SiN<sub>x</sub>, 300nm, Ref. 10: "passivated" TFTs,  $V_{GS} = 1.5$ V,  $V_{T0} = 2.7$ V, insulator: SiN<sub>x</sub>, 200nm. A relative dielectric constant of 7.5 and 3.9 was assumed for all nitride and oxide insulators, respectively. The threshold voltage shift of 1.5V marked on the plot corresponds to approximately 50% drop in the TFT currents.

increasing the gate nitride deposition temperature, using hydrogen dilution during the growth of the gate nitride and eventually the combination of both. We show that hydrogen dilution during the growth of *a*-Si:H is necessary for achieving high TFT lifetimes at low gate electric fields and discuss it in terms of the substrate dependence of *a*-Si:H growth.

## **5.4.1** Experiments: Increased Nitride Growth Temperature

The experimental results of Section 4.4 suggest that the a-Si:H TFT lifetime is improved by increasing the gate nitride deposition temperature from ~200°C to ~300°C. This was further studied in Section 5.2 and the improvement of the low field stability of a-Si:H TFTs by increasing the gate nitride deposition temperature was attributed to the improvement of the a-Si:H channel quality close to the a-Si:H/nitride interface. Our experiments show that without hydrogen dilution for a-Si:H growth, increasing the gate

nitride deposition temperature from 300°C (sample (c), Table 5.2) to 350°C (sample (g), Table 5.2) has negligible effect on low-field TFT stability (Fig. 5.7.Fig. 5.11). However, when hydrogen dilution is used for the growth of a-Si:H, increasing the gate nitride deposition temperature from 300°C (sample (f), Table 5.2) to 350°C (sample (h), Table 5.2) improves the TFT lifetime from  $\sim$ 10 years to  $\sim$ 100 years (Fig. 5.7.Fig. 5.11). The physical effect of the gate nitride and the role of hydrogen dilution during a-Si:H growth in improving the low field stability in these experiments are discussed in Section 5.4.4.

The a-Si:H TFT drive current half-life of  $\sim$ 100 years exceeds the luminance half-life ( $\sim$ 30 years) of high-quality OLEDs, suggesting that these TFTs may qualify for driving high-quality OLEDs in 2-TFT AMOLED pixels. However, due to the high nitride deposition temperature of 350°C, we have implemented this process only on glass. Plastic compatibility requires improving the nitride quality without further increasing the deposition temperature. This issue is addressed in the following section.

# **5.4.2** Experiments: Hydrogen Dilution for Nitride Growth

In the previous section, the deposition temperature of the gate nitride was increased to  $\sim 350^{\circ}\text{C}$  to improve quality of a-Si:H close to the a-Si:H/nitride interface and achieve a TFT lifetime of  $\sim 100$  years. However, a process temperature limit of 300°C is desired to improve the plastic compatibility. Our experiments show that hydrogen dilution can be used for the growth of the gate nitride to allow lower nitride deposition temperatures. As a result, a nitride deposition temperature of  $\sim 300^{\circ}\text{C}$  can be used to achieve a high TFT lifetime of  $\sim 100$  years (sample (i), Table 5.2).

As discussed in Section 3.3.2, the application of hydrogen dilution for improving the quality of nitride at low deposition temperatures ( $<200^{\circ}$ C) has been reported [23][24][25]. Earlier groups have also observed that hydrogen dilution affect the plasma properties during nitride growth at higher depositions temperatures as well and affect TFT stability, but no significantly high lifetimes (higher than  $\sim$ 1 month) were achieved with the growth conditions under study [26][27]. Our work is novel in that hydrogen dilution is used at high nitride deposition temperatures ( $\sim$ 300°C), not particularly to improve the quality of the nitride for high field properties but rather to improve the quality of a-Si:H close to the a-Si:H/nitride interface.

| Sample/Curve | a-SiN <sub>x</sub> :H De | eposition  | a-Si:H Dep  | Extrapolated |                |  |

|--------------|--------------------------|------------|-------------|--------------|----------------|--|

| Label        | Temperature              | H dilution | Temperature | H dilution   | Lifetime       |  |

| (c)          | ~ 300°C                  | No         | ~ 250°C     | No           | ~ 1 month      |  |

| (f)          | ~ 300°C                  | No         | ~ 250°C     | Yes          | ~ 10 years     |  |

| (g)          | ~ 350°C                  | No         | ~ 250°C     | No           | $\sim 1$ month |  |

| (h)          | ~ 350°C                  | No         | ~ 250°C     | Yes          | ~ 100 years    |  |

| (i)          | ~ 300°C                  | Yes        | ~ 250°C     | Yes          | ~ 100 years    |  |

| (j)          | ~ 350°C                  | Yes        | ~ 250°C     | Yes          | ~ 1000 years   |  |

**Table 5.2.** Deposition conditions of the *a*-Si:H channel and the gate nitride for the test TFTs studied in this section. The extrapolated lifetimes of these TFTs are also listed in the table. Samples (c) and (f) are repeated from Table 5.1 for comparison. All test TFTs are back-channel passivated.

# 5.4.3 Experiments: Hydrogen Dilution and Increased Temperature for Nitride Growth

Our experiments show that further improvement in the TFT lifetime is possible by raising the nitride deposition temperature and using hydrogen dilution for the growth of both the *a*-Si:H channel and the gate nitride. With a process temperature of 350°C for the gate nitride (sample (j), Table 5.2), we have demonstrated a TFT lifetime of ~1000 years (Fig. 5.7.Fig. 5.11). The drive current half-life of ~1000 years is well above the luminance half-life of high-quality OLEDs (~30 years), showing the promise of these TFTs for driving high-quality OLEDs in 2-TFT AMOLED pixels.

## 5.4.4 Physical Effect of Gate Nitride on *a*-Si:H Channel

As discussed in Section 3.2, in the bottom-gate *a*-Si:H TFT structure, *a*-Si:H is deposited on top of the gate nitride. Therefore the quality and microstructure of *a*-Si:H can be affected by that of the nitride underneath it. Substrate dependence of *a*-Si:H growth is well-known especially when hydrogen dilution is included during PECVD growth typically intended for the growth of nanocrystalline Si (nc-Si) or microcrystalline Si (μc-Si) which are of interest for both TFT and solar cell applications [13][14][28].

In general, it is well-established that for amorphous substrates such as glass, metal or plastic, sufficiently high [H<sub>2</sub>]/[SiH<sub>4</sub>] ratios (about 10 and above) lead to the growth of

nc/μc-Si after an *a*-Si:H transition layer (in which random nucleation takes place) is grown [13][14]. The thickness of the transition layer is substrate dependent and is reduced by increasing the hydrogen dilution ratio. For example, with [H<sub>2</sub>]/[SiH<sub>4</sub>]=15, the thickness of the *a*-Si:H transition layer was found to be ~100nm and ~300nm on silicon dioxide (SiO<sub>2</sub>) and *a*-Si:H substrates, respectively. With [H<sub>2</sub>]/[SiH<sub>4</sub>]=40, nc/μc-Si was found to grow immediately on SiO<sub>2</sub> (i.e. with no initial *a*-Si:H transition layer growth), while an *a*-Si:H transition layer of 20nm was still observed on *a*-Si:H substrates at the same [H<sub>2</sub>]/[SiH<sub>4</sub>] of 40. For immediate growth of nc/μc-Si:H on *a*-Si:H, the required [H<sub>2</sub>]/[SiH<sub>4</sub>] is extrapolated to be as high as 1000 (which are not practical for film growth) [13][14]. These observations clearly indicate that an underlying substrate, even if of amorphous nature, can have a significant effect on the quality and microstructure of *a*-Si:H which is grown on that substrate. The substrate dependence of nc/μc-Si:H growth is also well-known [28]

The substrate dependence of growth is even more pronounced if a nano/micro-crystalline, polycrystalline or single crystalline substrate is used instead of an amorphous substrate. For example, in the case of a single-crystalline substrate such as a Si wafer,  $[H_2]/[SiH_4]$  ratios of ~10 and higher result in immediate epitaxial growth of single-crystalline Si on the wafer [29][30]. However, eliminating or lowering the hydrogen dilution results in the growth of a-Si:H rather than single-crystalline Si, further highlighting the role of hydrogen dilution, which can be explained within the context of Fig. 5.9. Hydrogen radicals remove the weak Si-Si bonds (which would otherwise result in the growth of an amorphous film) in-situ from the growth surface, leaving only the strong Si-Si bonds, and therefore leading to the growth of a single-crystalline film following the crystalline structure of the Si substrate.

The improvement in the low-field lifetime of our test TFTs with improving the nitride quality when hydrogen dilution is used for growing the a-Si:H channel (samples (f), (h), (i) and (j), Table 5.2) from  $\sim$ 10 years to  $\sim$ 1000 years is a clear indication that the gate nitride quality affects the quality of the a-Si:H channel material grown on top of it. The role of hydrogen dilution is also evident as the lifetime of the test TFTs fabricated with no hydrogen dilution for the growth of the a-Si:H channel is lower than a month (samples (c) and (g), Table 5.2). Our work is novel in that we use an "amorphous"

**Fig. 5.11.** Normalized TFT current vs. time for various a-Si:H TFTs grown at different conditions listed in Table 5.2. The stress conditions are the same as that illustrated in Fig. 5.3 (a). The current drop of a conventional a-Si:H TFT is also included from the literature as a reference [11].

material (nitride) as a growth template to improve the quality of another "amorphous" material (*a*-Si:H) grown on top of it (rather than growing nano/microcrystalline films). The extracted electron mobility of our test TFTs (of the order ~1cm<sup>2</sup>/Vs for long-channel devices) confirms that the channel is still amorphous.

## 5.5 Summary and Conclusion

In this chapter, the stability requirement on *a*-Si:H TFTs for driving OLEDs was discussed and the stability of conventional *a*-Si:H TFTs was shown to be too short was driving OLEDs. To improve the stability of *a*-Si:H TFTs, the mechanisms responsible for the threshold voltage shift in these devices were studied. The instability mechanisms were identified by measuring the time-dependence and field dependence of the TFT threshold voltage shift. At low gate electric fields required for driving OLEDs, the creation of defects in *a*-Si:H and electron trapping into these defects was found to be the dominant instability mechanism. The quality of *a*-Si:H close to the *a*-Si:H/nitride interface which determines the rate of defect creation in *a*-Si:H was found to depend on both the *a*-Si:H channel and the gate nitride. Including hydrogen dilution during the

growth of *a*-Si:H and the gate nitride, and a high temperature for the growth of the gate nitride was demonstrated to improve the drive current half-life of standard *a*-Si:H TFTs from lower than a month to over 1000 years, well above the luminance half-life of high-quality OLEDs (~30 years). This suggests that the improved *a*-Si:H TFTs may qualify for driving OLEDs for commercial display applications.

## References:

- [1] Private Communication with Michael Hack of Universal Display Corporation, Ewing, NJ 08618, USA

- [2] B. W. D'Andrade, "White PHOLED for Lighting", *Proceedings of the Annual Laser and Electro-Optics Society (LEOS) Meeting*, pp. 59-60, October 2007

- [3] F. B. McLean, "A direct tunneling model of charge transfer at the insulator-semiconductor interface in MIS devices", U.S. Government Report HDL-TR-1765, October 1976

- [4] R. H. Walden, "A Method for the Determination of High-Field Conduction Laws in Insulating Films in the Presence of Charge Trapping", *Journal of Applied Physics*, vol. 43, no. 3, pp. 1178-1186, March 1972

- [5] F. R. Libsch and J. Kanicki, "Bias-stress-induced stretched-exponential time dependence of charge injection and trapping in amorphous thin-film transistors", *Applied Physics Letters*, vol. 62, no. 11, pp. 1286-1288, March 1993

- [6] Ke Long, "Towards Flexible Full-Color Active Matrix Organic Light-Emitting Displays: Dry Dye Printing for OLED Integration and 280oC Amorphous-Silicon Thin-Film Transistors on Clear Plastic Substrates", Ph.D. Dissertation: Princeton University, March 2006

- [7] Kunigunde H. Cherenack, "Fabricating Silicon Thin-Film Transistors on Plastic at 300°C", Ph.D. Dissertation: Princeton University, December 2009

- [8] M. J. Powell, C. van Berkel, and J. R. Hughes, "Time and temperature dependence of instability mechanisms in amorphous silicon thin-film transistors", *Applied Physics Letters*, vol. 54, no. 14, pp. 1323-1325, April 1989

- [9] W. B. Jackson and M. D. Moyer, "Creation of near-interface defects in hydrogenated amorphous silicon-silicon nitride heterojunctions: The role of hydrogen", *Physical Review B*, vol. 36, no. 11, pp. 6217-6220, October 1987

- [10] M. J. Powell, C. Berkel, A. R. Franklin, S. C. Deane, and W. I. Milne, "Defect pool in amorphous-silicon thin-film transistors," *Physical Review B*, vol. 45, no. 8, pp. 4160–4170, Feb. 1992

- [11] K. S. Karim, A. Nathan, M. Hack and W. I. Milne, "Drain-bias dependence of threshold voltage stability of amorphous silicon TFTs", *IEEE Electron Device Letters*, vol. 25, no. 4, pp. 188-190, April 2004

- [12] S. M. GadelRab and S. G. Chamberlain, "Improvement of the reliability of amorphous silicon transistors by conduction-band tail width reduction", *IEEE Transactions on Electron Devices*, vol. 45, no. 10, pp. 2179-2186, October 1998

- [13] J. Koh, A. S. Ferlauto, P. I. Rovira, C. R. Wronski, and R. W. Collins, "Evolutionary phase diagrams for plasma-enhanced chemical vapor deposition of

- silicon thin films from hydrogen-diluted silane", *Applied Physics Letters*, vol. 75, no. 15, pp. 2286-2288, October 1999

- [14] A. S. Ferlauto, R. J. Koval, C. R. Wronski, and R. W. Collins, "Extended phase diagrams for guiding plasma-enhanced chemical vapor", *Applied Physics Letters*, vol. 80, no. 15, pp. 2666-2668, April 2002

- [15] I-C. Cheng and S. Wagner, "Hole and electron field-effect mobilities in nanocrystalline silicon deposited at 150°C", *Applied Physics Letters*, vol. 80, no. 3, pp. 2666-2668, January 2002

- [16] Y. Chen and S. Wagner, "Inverter made of complementary p and n channel transistors using a single directly deposited microcrystalline silicon film", *Applied Physics Letters*, vol. 75, no. 8, pp. 1125-1127, August 1999

- [17] M. Konumaab, H. Curtinsac, F-A. Sarotta and S. Vepřeka, "Dependence of electrical conductivity of nanocrystalline silicon on structural properties and the effect of substrate bias", *Philosophical Magazine B*, vol. 55, no. 3, pp. 377-389, July 1986

- [18] K. Girotra, Y-M. Choi, B-J. Kim, Y-R. Song, B. Choi, S-H. Yang, S. Kim, S. Lim, "PECVD-based nanocrystalline-silicon TFT backplanes for large-sized AMOLED Displays", *Journal of the Society for Information Display*, Vol. 15, no. 2, pp. 113-118, February 2007

- [19] C-H. Lee, D. Striakhilev and A. Nathan, "Stability of nc-Si:H TFTs With Silicon Nitride Gate Dielectric", *IEEE Electron Device Letters*, vol. 54, no. 1, pp. 45-47, January 2007

- [20] R. B. Wehrspohn, S. C. Deane, I. D. French and M. J. Powell, "Stability of plasma deposited thin film transistors comparison of amorphous and microcrystalline silicon", Thin Solid Films, vol. 383, nos. 1-2, pp. 117-121, February 2001

- [21] I. D. French, S. C. Dean, D. T. Murley, J. Hewett, I. G. Gale and M. J. Powell, "The effect of the amorphous silicon alpha–gamma transition on thin film transistor performance", *Materials Research Society Symposium Proceedings*, vol. 467, pp. 875-880, April 1997

- [22] R. B. Wehrspohn, S. C. Deane, I. D. French, J. Hewett and M. J. Powell, "Stability of amorphous silicon thin film transistors", *Materials Research Society Symposium Proceedings*, vol. 557, pp. 365-370, April 1999

- [23] C. McArthur, M. Meitine and Andrei Sazonov, "Optimization of 75°C Amorphous Silicon Nitride for TFTs on Plastics", *Materials Research Society Symposium Proceedings*, vol. 769, pp. H9. 8. 1-6, April 2003

- [24] C. S. Yang, L. L. Smith, C. B. Arthur, and G. N. Parsons, "Stability of low-temperature amorphous silicon thin film transistors formed on glass and transparent plastic substrates", *Journal of Vacuum Science and Technology B*, vol. 18, no. 2, pp. 683-689, March 2000

- [25] H. Gleskova, S. Wagner, V. Gasparik, P. Kovac, "Low-temperature silicon nitride for thin-film electronics on polyimide foil substrates", *Applied Surface Science*, vols. 175-176, pp. 12-16, May 2001

- [26] I. D. French, C. J. Curling and A. L. Goodyear, "Silicon nitride optimization for a-Si:H TFTs used in projection LC-TVs", *Materials Research Society Symposium Proceedings*, vol. 336, pp. 769-774, April 1994

- [27] B. Dunnett, C. H. Cooper, D. T. Murley, R. A. G. Gibson, D. Jones, M. J. Powell, S. C. Deane and I. D. French, "Equilibration in amorphous silicon nitride alloys", Materials Research Society Symposium Proceedings, vol. 337, pp. 349-354, April 1995

- [28] P. R. Cabarrocas, N. Layadi, T. Heitz, B. Drevillon and I. Solomon, "Substrate selectivity in the formation of microcrystalline silicon: Mechanisms and technological consequences", *Applied Physics Letters*, vol. 66, no. 26, pp. 3609-3611, January 1995

- [29] K. Yamamoto, T. Suzuki, K. Kondo, T. Okamoto, M. Yamaguchi, M. Izumina, Y. Tawada, "Low temperature Si crystal growth by alternating deposition and hydrogen etching sequences and its application to the p-layer of *a*-Si:H solar cells", *Solar Energy Materials and Solar Cells*, vol. 34, nos. 1-4, pp. 501-508, September 1994

- [30] J. Damon-Lacostea and P. R. Cabarrocas, "Toward a better physical understanding of *a*-Si:H/c-Si heterojunction solar cells", *Journal of Applied Physics*, vol. 105, no. 6, pp. 063712-1-7, March 2009

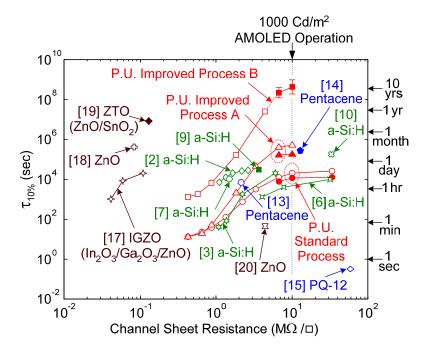

# Trade-off Regimes of Lifetime in a-Si:H Thin-Film Transistors and a Universal Lifetime Comparison Framework

In the previous chapters, the *a*-Si:H TFT lifetime was studied in the context of the TFT current decay versus time or versus the gate electric field. Changing the TFT structural parameters such as the gate insulator thickness will change both the TFT current and the rate of degradation, making it difficult to compare different designs. However, comparing lifetime versus channel sheet resistances, as shown this chapter, is not affected by changes in TFT parameters. Studying the *a*-Si:H TFT lifetime versus channel sheet resistance identifies two modes of degradation which are explained in terms of their physical origins and modeled quantitatively in this chapter. These modes of degradation demonstrate that there is a trade-off between high TFT drive current and high-lifetime, both of which are desirable design parameters. Based on these studies, a universal lifetime comparison framework is presented for *a*-Si:H TFTs as well as other TFT technologies.

# 6.1 Current Decay Modes and Lifetime Regimes

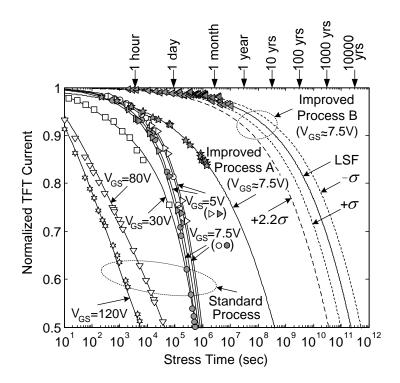

The TFT current decay for the "standard" and "improved" a-Si:H TFTs and at drain-source voltages of 0.1V (for gate voltages up to 120V) in the linear regime and a drain-source voltage of 15V (for gate voltages up to 10V) in saturation are plotted in Fig. 6.1 ("Standard Process" refers to no hydrogen dilution for a-Si:H and gate nitride growth (process (c), Table 5.2), "Improved Process A" refers to hydrogen dilution only for a-Si:H growth (process (f), Table 5.2) and "Improved Process B" refers to hydrogen dilution for both a-Si:H and gate nitride growth (process (j), Table 5.2)). Because the current decays faster (lifetime is lower) at high gate voltages (low channel sheet resistance), from an application point of view, it is useful to examine the lifetime vs. channel sheet resistance. The channel sheet resistance ( $R_{sheet}$ ) is defined as  $(V_{DS}/I_{TFT,lin}) \cdot (L/W)$ , where  $V_{DS}$  is the drain-source voltage,  $I_{TFT,lin}$  the TFT current in the linear mode, L the channel length and W the channel width. The reason for choosing channel sheet resistance instead of gate voltage is that the drain current and circuit delay

**Fig. 6.1.** Degradation of *a*-Si:H TFT current in the linear (empty symbols) and saturation mode (full symbols). The lines are predictions based on Eq. (6.3) and (6.5). The "Standard Process", "Improved Process A" and "Improved Process B" refer to processes (c), (f) and (j) in Table 5.2, respectively. The dashed lines show the error bounds for the least square fit (LSF) used for the improved process B.

can be determined directly from the channel sheet resistance without being affected by changes in the gate insulator capacitance, carrier mobility and initial threshold voltage.

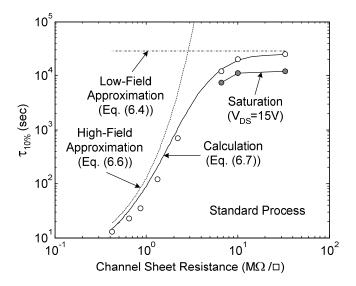

The lifetime for a 10% decay of current (denoted as  $\tau_{10\%}$  in Fig. 6.2) from the data of Fig. 6.1 (for the standard TFT process) shows two different regimes. At low channel sheet resistance there is a trade-off between high lifetime and low channel sheet resistance (both desirable device parameters). At high channel sheet resistance, the lifetime becomes independent of channel sheet resistance.

## 6.2 Physical Origin of Lifetime Regimes

To understand the physical origin of the two regimes, the TFT threshold voltage rise  $(\Delta V_T)$  is extracted from the decay of current (Fig. 6.3), assuming negligible shift in mobility and other TFT parameters [4][5][6]. First-order TFT equations are assumed in the linear (with small  $V_{DS}$ ) and saturation regimes (Section 3.2)

Chapter 6: Trade-off Regimes of Lifetime in a-Si:H Thin-Film Transistors ...

$$I_{TFT,lin}(t) = \mu_{FE} C_{ins} \frac{W}{L} (V_{GS} - V_{T0} - \Delta V_{T,lin}(t)) V_{DS}$$

(6.1a)

$$I_{TFT,sat}(t) = \frac{1}{2} \mu_{FE} C_{ins} \frac{W}{L} (V_{GS} - V_{T0} - \Delta V_{T,sat}(t))^{2}$$

(6.1b)

where  $V_{GS}$  is the gate-source voltage,  $V_{T0}$  the initial threshold voltage,  $\mu_{FE}$  the field-effect mobility of carriers (electrons), and  $C_{ins}$  the gate dielectric capacitance per unit area, i.e.  $\varepsilon_{ins}/t_{ins}$ , where  $\varepsilon_{ins}$  and  $t_{ins}$  are the dielectric constant and thickness of the gate dielectric ( $\varepsilon_{ins} = 7.4\varepsilon_0$  for nitride). The subscripts "lin" and "sat" refer to the linear and saturation modes, respectively. For our standard a-Si:H TFTs ( $L = 5\mu m$ ),  $\mu_{FE} = 0.64 \pm 0.05 \text{ cm}^2/\text{Vs}$  and  $V_{T0} = 2.2 \pm 0.2 \text{ V}$ .

Qualitatively, the two regimes may be understood as follows. The TFT threshold voltage shift is caused by the channel electrons trapped into the gate nitride or the defects created in the a-Si:H channel [4][5]. In either case, channel sheet resistance increases with the drop in the number of mobile channel electrons,  $n_{chan}$  (note  $n_{chan} = C_{ins}(V_{GS} - V_T) = C_{ins}(V_{GS} - V_{T0}) + Q_{trap}/q$ , where  $V_T$  is the TFT threshold voltage,  $Q_{trap}$  the trapped charge ( $Q_{trap} < 0$ ) and q the electron charge). Therefore the fractional

**Fig. 6.2.** The 10% current decay lifetime  $(\tau_{10\%})$  vs. channel sheet resistance  $(1/[\mu_{FE} C_{ins}(V_{GS} - V_{T0})])$  for our standard TFTs (process (c) in Table 5.2) along with the high and low field approximations and calculation for the linear mode. Empty and full symbols indicate the linear and saturation modes, respectively.

change in channel sheet resistance is

$$\frac{\Delta R_{sheet}}{R_{sheet}} \approx \frac{-\Delta n_{chan}}{n_{chan}} \propto \frac{-Q_{trap}/\varepsilon_{ins}}{n_{chan}} \propto \frac{-Q_{trap}/\varepsilon_{ins}}{E_{ins}}$$

(6.2)

where  $E_{ins}$  is the gate electric field, defined as  $V_{GS}/t_{ins}$ . For the last term we assume the trapped charge is small compared to the channel charge (so  $n_{chan}$  is the dominant source of  $E_{ins}$ ), as would be valid when the current decays is less than 10% of its initial value (implying the channel charge has been reduced by less than 10%). In writing Eq. (6.2), we assume the gate insulator is thick compared to the a-Si:H/nitride interface region where charge trapping occurs). At low gate electric fields ( $V_{GS} < \sim 7.5 \text{V}$  for our nitride thickness), the threshold voltage shift is dominated by defect creation in a-Si:H and electron trapping in these defects. The rate of this process (and thus the trapped charge) and the shift of the channel sheet resistance are proportional to the number of mobile channel electrons [6]. Thus the fractional change in the channel sheet resistance (and thus the TFT lifetime) is independent of the channel sheet resistance in this regime, explaining the observation in Fig. 6.2. At high gate fields ( $V_{GS} > \sim 30 \text{V}$ ), the threshold voltage shift is dominated by charge trapping in the PECVD gate nitride, where Fowler-Nordheim tunneling is dominant at room temperature [1], resulting in an approximately quadratic dependence on the gate electric field,  $E_{ins}$  [8]. Therefore at high gate fields,  $\Delta R_{\it sheet} \, / \, R_{\it sheet} \propto E_{\it ins}$  . The TFT lifetime drops with increasing the gate electric field (lowering the channel sheet resistance), again consistent with Fig. 6.2.

#### 6.3 Quantitative Model of Lifetime Regimes

The two regimes of lifetime may be quantitatively modeled as follows. In the low-field regime (referred to by the subscript " $low-V_{GS}$ "), the threshold voltage shift may be approximated by a power law [4][5] ( $\beta$  and  $\tau_0$  are constants).

$$\Delta V_{T,lin,low-V_{GS}} = (V_{GS} - V_{T0}) \cdot (t/\tau_0)^{\beta}$$

$$(6.3)$$

The saturation regime is important at low fields because it is the realistic operation regime for driving OLEDs. In this regime,  $\Delta V_{T,sat,low-V_{GS}} = (2/3)\Delta V_{T,lin,low-V_{GS}}$  as the density of mobile channel electrons is lower by a factor of 2/3 compared to the linear mode [6].

**Fig. 6.3.** Threshold voltage shifts of *a*-Si:H TFTs extracted from Fig. 6.1. The models (lines) are based on Eq. (6.3) and (6.5). Empty and full symbols refer to the linear and saturation modes, respectively. The 0.27V and 1.5V shifts correspond to 10% and 50% current drop at  $V_{GS} = \sim 7.5$ V in saturation. The dashed lines show the error bounds for the least square fit (LSF) used for the improved process B.

For our standard TFTs,  $\beta = 0.45$  and  $\tau_0 = 2.8 \times 10^6 \, \text{sec}$ . Using Eq. (6.3) and (6.1a), the low-field lifetime in the linear regime is found as

$$\tau_{10\%, lin, low-V_{GS}} = \tau_0 (0.1)^{1/\beta} \tag{6.4}$$

Using Eq. (6.1b) and Eq. (6.3) (including the 2/3 factor for the latter), the low-field lifetime in saturation is found to be lower than that in the linear regime by a factor of  $[(2/3).(1+\sqrt{0.9})]^{1/\beta}$ . This is because of a higher sensitivity of the TFT current to the TFT threshold voltage in saturation. In the high-field regime (referred to by the subscript "high- $V_{GS}$ "),  $\Delta V_T$  is logarithmic in time [1][3] (B and  $t_0$  are constants).

$$\Delta V_{T,lin,high-V_{GS}} \approx B \cdot V_{GS}^{2} \cdot \ln(1 + t/t_0)$$

(6.5)

For our standard TFTs,  $t_0 = 4.7 \,\text{sec}$  and  $B = 5.8 \times 10^{-4} \,\text{V}^{-1}$ . Thus the high field lifetime can be found from Eq. (6.5) and (6.1a)

Chapter 6: Trade-off Regimes of Lifetime in a-Si:H Thin-Film Transistors ...

$$\tau_{10\%, lin, high-V_{GS}} \approx t_0 \exp(0.1/BV_{GS})$$

(6.6)

When both degradation mechanisms are important,  $\tau_{10\%}$  may be calculated numerically

$$(V_{GS} - V_{T0}) \cdot (\tau_{10\% lin} / \tau_0)^{\beta} + B \cdot V_{GS}^{2} \cdot \ln(1 + \tau_{10\% lin} / t_0) = 0.1(V_{GS} - V_{T0})$$

(6.7)

This model fits the data quantitatively (Fig. 6.2).

## 6.4 Process Dependence of Lifetime Regimes

The two lifetime regimes are present for the improved a-Si:H TFTs as well. The quality of a-Si:H may be improved by "in situ" removal of weak Si-Si bonds by including hydrogen dilution during the PECVD of a-Si:H and using a back-channel passivated TFT structure. Replacing the standard a-Si:H with the improved a-Si:H (improved process A), improves the lifetime at high channel sheet resistance (red triangles in Fig. 6.4), as a result of a lower defect creation rate in the improved a-Si:H.

Improving the quality of the gate nitride in addition to improving the *a*-Si:H channel (improved process B) further improves the lifetime at both high and low channel

**Fig. 6.4.** The 10% current decay lifetime vs. channel sheet resistance for our *a*-Si:H TFTs (P.U. refers to "Princeton University" and the error bars indicate the standard deviations of fitting errors), along with those of *a*-Si:H TFTs and other TFT technologies from other groups. Empty and full symbols refer to the linear and saturation modes, respectively.

sheet resistance (red squares in Fig. 6.4). This was achieved by using a high deposition temperature (350°C) and including hydrogen dilution during the PECVD of the gate nitride for the "in situ" removal of weakly bonded Si atoms. The improvement at high fields is due to lower charge trapping in the improved nitride as a result of a lower density of nitride traps. The improvement at low-fields may be due to an improved *a*-Si:H quality close to the *a*-Si:H/nitride interface. Since *a*-Si:H is deposited after the gate nitride, the quality of *a*-Si:H may be affected by that of the nitride underneath it. For both improved processes, the two distinct lifetime regimes are clearly evident.

A low gate voltage of ~7.5V (corresponding to  $V_{GS} - V_{T0} = 5.3$  V,  $E_{ins} \approx 2.5 \times 10^5$  V/cm and  $R_{sheet} = 10 \text{M}\Omega/\square$ ) is required for driving high quality OLEDs at a luminance of  $1000 \text{Cd/m}^2$  in a typical AM-OLED design (see section 4. 2). The current degradation of the improved a-Si:H TFTs at these drive conditions in saturation are plotted in Fig. 6.1 ( $V_{T0} = 2.4 \pm 0.2$  V and  $2.6 \pm 0.2$  V for the improved processes A and B, respectively). The threshold voltage shifts are extracted from the current degradation and extrapolated based on Eq. (6.3) (including the 2/3 factor) using linear least square fits (Fig. 6.3). These fits are then used to extrapolate the current degradation in Fig. 6.1 using Eq. (6.1b). The upper and lower error bounds corresponding to the standard deviation of errors in the least square fit (+ $\sigma$  and - $\sigma$ ) are also plotted for the improved process B. An upper error bound of 2.2 times the standard deviation (+2.2 $\sigma$ ) corresponds to 2 years and 1000 years of lifetime for 10% and 50% current decay, respectively. Assuming a normal distribution of errors, the +2.2 $\sigma$  bound indicates a confidence of ~ 99% (~ 1% error) in prediction.

#### 6.5 Universal Lifetime Comparison Framework

The presence of the two lifetime regimes for different *a*-Si:H TFT processes developed in our lab suggests that plotting the current decay lifetime versus the TFT channel sheet resistance can be used as a framework for comparing the lifetime of *a*-Si:H TFTs fabricated with different structures, process technologies or growth conditions. In this section, this is verified by plotting the *a*-Si:H TFT data from the literature in the context of this comparison framework. Next, it is shown that this comparison framework can be used for other TFT technologies as well.

#### **6.5.1** Comparison with other *a*-Si:H TFTs

Converting the published plots of threshold voltage shift vs. time to current decay for *a*-Si:H TFTs reported in the literature [3][6][2][7][9][10] shows that at low fields (high channel sheet resistances), the lifetimes of our standard *a*-Si:H TFTs (red circles in Fig. 6.4) and those reported in the literature (green symbols in Fig. 6.4) are comparable. Our improved *a*-Si:H TFTs have significantly higher lifetimes, especially in the high-channel resistance regime, which is the one appropriate for driving OLEDs. This improvement is due to low defect creation rates in *a*-Si:H (and therefore more stable threshold voltages) as indicated from both small values of  $\beta$  (0.22 and 0.26 for the improved processes A and B, respectively, vs. 0.45 for the standard process) and large values of  $\tau_0$  (1.1×10<sup>8</sup> and 4×10<sup>10</sup>, vs. 2.8×10<sup>6</sup> sec) extracted from the fits in Fig. 6.3. The low  $\beta$  of the improved TFTs physically corresponds to a sharper low energy tail of the distribution of bond energies, i.e. a lower density of weak bonds and thus a more stable material [5][11]. The large  $\tau_0$  implies a lower attempt frequency for bond breaking [11][12], which can be explained by a larger localization length of the electron wave-function in the case of stronger Si-Si bonds [12].

#### **6.5.2** Comparison with other TFT Technologies

This comparison framework of lifetime vs. channel sheet resistance is more general than a-Si:H TFTs and can be applied to other TFTs as well. In contrast to direct comparison of threshold voltage stability, this approach is not affected by the different values of mobility, gate insulator capacitance, initial threshold voltage as well as the different values of gate stress voltages used for the TFTs being compared. The lifetime of various TFTs reported in the literature including organic [13][14][15] and metal-oxide devices [16][17][18][19] are given in Fig. 6.4 above. These lifetimes were determined by inspecting the published plots of TFT current decay vs. time or converting the published plots of TFT threshold voltage shift vs. time to plots of current decay, using Eq. (6.1a) or (6.1b) based on the TFT operation mode. A first-order extrapolation in time was performed on the data when necessary. Organic devices generally fall to the right due to their low mobilities and in the best case have a lifetime of  $\sim$ 3 days at a channel sheet resistance of 12.8 M $\Omega$ / $\square$ , several orders of magnitude below high-lifetime a-Si:H TFTs.