Jim STORM

# 1999 Silicon Nanoelectronics Workshop

June 12 - 13, 1999

Rihga Royal Hotel Kyoto, Kyoto, Japan

Workshop Abstracts

## Doped and Undoped SiGeC Layers for Dopant Profile Control in sub-100 nm Vertical MOSFET's

J. C. Sturm, M. Yang, and M. S. Carroll

Department of Electrical Engineering, Center for Photonics and Optoelectronic Materials

Princeton University, Princeton, NJ 08544 USA

609-258-5610, fax: 609-258-1954, sturm@ee.princeton.edu

#### Introduction/Abstract

Vertical FET structures are of interest because they allow short channel lengths to be defined without lithography, and can be gated from two-sides if the pillar is thin. Such doublegated (or wrap-around) gates of low off-currents possibility at room temperature and allow one to eliminate channel doping (and the resulting statistical fluctuation problems) [1,2]. In this work the use of Si<sub>1-x-</sub> <sub>v</sub>Ge<sub>x</sub>C<sub>v</sub> layers is explored to make vertical structures stable to thermal processing (e.g. sidewall gate oxide growth or implantation annealing), and the method is demonstrated with sub 100-nm p-channel FET's.

#### **Diffusion Control and Device Results**

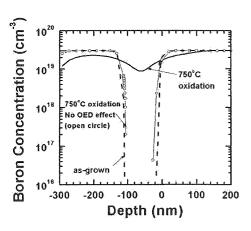

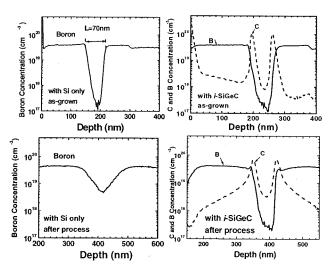

Fig. 1 shows a process simulation of how severely a 750°C wet oxidation step causes boron to diffuse from a pre-defined vertical FET structure with a channel length of 110 nm, which clearly makes any device impossible. If one

Fig.1. Simulation of boron diffusion in a 110nm vertical p-channel FET with oxidation enhanced diffusion turned on and off (750°C, 40min).

artificially turns off the oxidation-enhanced diffusion (OED) in the simulator, sub-100nm devices become possible. Similar results would occur from transient-enhanced-diffusion (TED) during low-temperature annealing of conventional ion implantations performed above the FET structure due to defect migration. Over the last few years, it has been shown that low levels of C in Si<sub>1-y</sub>C<sub>y</sub> or Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> (<1%C) are effective at gettering Si interstitial atoms, and thus reducing the OED and TED effects [3,4]. The diffusion of B can be reduced some distance from the actual Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> layers (Fig. 2).

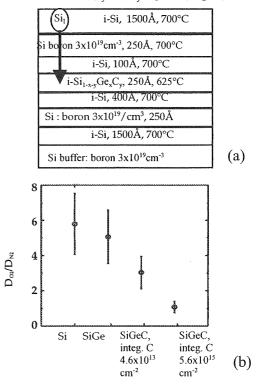

Fig. 2. (a) Buried marker structure to study ability of SiGeC to getter interstitials and reduce OED; (b) relative B diffusion coefficient in  $O_2$  vs.  $N_2$  in lower B layer under 850°C oxidation as function of C levels in the SiGeC blocking layer.

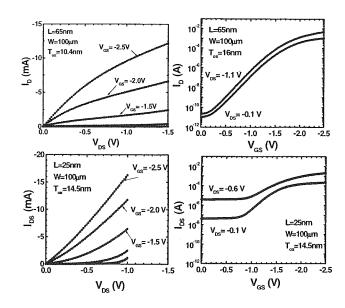

Therefore undoped 20nm SiGeC layers  $(20\% \text{ Ge}, \sim 0.4\%\text{C})$  were inserted into the channel next to S/D (Fig. 3) or p+ doped SiGeC layers were inserted into the S/D itself to curb boron diffusion. The device structures were made by growing the entire source/channel/drain structure by RTCVD epitaxy at 625-750°C, since the channel length is then directly controlled and does not depend on etch times, etc. Only wide pillar devices with phosphorusdoped channels (~2x10<sup>18</sup>cm<sup>-3</sup> with ~15nm/ decade profile control) have been made to date. Various tradeoffs of doped vs. undoped SiGeC and channel designs will be discussed. Nearly ideal devices can be made at channel lengths well under 100 nm, far shorter than previous bests for p-channel devices of 200 nm for S/D implantation after gate oxidation[6] and 140nm for 600°C oxides at high pressure with epitaxially grown S/D's [7]. Note leakage currents remain very low even with the SiGeC (Fig. 4). Devices with L of 25 nm are reasonable above threshold, but suffer from punchthrough below threshold.

Fig. 3. SIMS profiles of vertical p-channel FET structures both before and after sacrificial and gate oxidation (750°C, 40min total) for all silicon and undoped  $\mathrm{Si}_{1\text{-}x\text{-}y}\mathrm{Ge}_x\mathrm{C}_y$  boron barriers (20nm) just outside the S/D in the channel.

Fig. 4. Linear and subthreshold characteristics for L = 65 nm and L = 25 nm vertical p-channel FET's.

### **Summary**

Si<sub>1-x-y</sub>Ge<sub>x</sub>C<sub>y</sub> layers can be effectively used to dramatically improve control of dopant profiles in short-channel devices, making them more tolerant of thermal processing. This can be achieved without a penalty of increased leakage. Current work in progress is attempting to combine these results with dual-gate structures, and to exploring the ability to minimize the diffusion of n-type dopants as well. The support of ONR and DARPA is gratefully acknowledged.

- 1. C. Auth and J. Plummer, IEEE Electron Device Lett. 18, 74, (1997).

- 2. D. J. Frank, S. E. Laux and M. V. Fischetti, IEDM Tech. Dig., 553, (1992).

- 3. P. A. Stolk, D. J. Eaglesham, H. J. Gossmann and J. M. Poate, Appl. Phys. Lett. <u>66</u>, 1370, (1995).

- 4. M. S. Carroll, C. L. Chang and J. C. Sturm, Appl. Phys. Lett. <u>73</u>, 3695, (1998).

- 5. M. Yang, C. L. Chang, M. Carroll and J. C. Sturm, IEEE Electron Device Lett. (June, 1999).

- 6. K. Liu, S. Ray, S. Oswal and S. Banerjee, IEEE Electron Device Lett. 19, 13, (1998).

- D. Behammer, L. Vescan, R. Loo, J. Moers, A. Muck, H. Luth and T. Grabolla, Electronics Lett. 32, 406, (1996).