# 1989 SOS/SOI TECHNOLOGY WORKSHOP

October 3-5, 1989

## AGENDA

Monday, October 2

.

| 8:00-10:00 pm | Conference Registration   |

|---------------|---------------------------|

|               | Wine and cheese reception |

| <u>Tuesday,</u> | October 3                                                                                                                                                                                                                                                                  |                                                                                                 |    |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----|

| 7:00-8:00       | ) am                                                                                                                                                                                                                                                                       | Continental Breakfast                                                                           |    |

| 7:50-8:00       | ) am                                                                                                                                                                                                                                                                       | <b>INTRODUCTORY COMMENTS:</b> JP. Colinge, G.E. Davis, M.T. Duffy                               |    |

| 8:00-11:0       | )0 am                                                                                                                                                                                                                                                                      | SESSION I: DEVICE MODELING AND PHYSICS                                                          | 12 |

|                 |                                                                                                                                                                                                                                                                            | Session Co-Chairmen: S. Cristoloveanu and P. Roitman                                            |    |

| 1.1             |                                                                                                                                                                                                                                                                            | mization of Silicon Film Thickness in Thin-Film SOI Devices"<br>e and M. Tack<br>en,Belgium)    | 13 |

| 1.2             | "Substrate Bias and Temperature Dependence of Anomalous Substhreshold<br>Slopes in Fully-Depleted Submicron SOI MOSFET's"<br>K. Tokunaga<br>(Hitachi Ltd., Tokyo, Japan)<br>J. C. Sturm<br>(Princeton University, Princeton, NJ)<br>JP. Colinge<br>(IMEC, Leuven, Belgium) |                                                                                                 | 15 |

| 1.3             | J.B. McKitte                                                                                                                                                                                                                                                               | in Breakdown in Thin SOI Transistors"<br>erick<br>al Aerospace Technology Center, Columbia, MD) | 17 |

| 1.4             | J.C.S. Woo                                                                                                                                                                                                                                                                 | v                                                                                               | 19 |

1

\_\_\_\_\_

9:20-9:40 <u>COFFEE BREAK</u>

| 1.5       | D.J. Wouters                                             | d Current in Thick and Thin-Film SOI MOSFET Transistors"<br>s, JP. Colinge and H.E. Maes<br>en, Belgium)                                                                                                     | 21       |

|-----------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.6       | JY. Choi a<br>(University of<br>R. Sundaresa             | for Submicron CMOS"<br>nd J.G. Fossum<br>of Florida, Gainesville, FL)<br>an<br>uments, Dallas, TX)                                                                                                           | 23       |

| 1.7       | F. Balestra,                                             | nd Simulation of Single and Double Gate Thin Film SOI MOSFETs"<br>M. Benachir, J. Brini, I. Sweid, G. Ghibaudo and N. Guillemot<br>IPG, Grenoble-Cedex, France)                                              | 25       |

| 1.8       | D. Flandre a                                             | er Analytical Modeling of Thin-Film SOI MOSFET's"<br>nd R. Van de Wiele<br>Catholique, Louvain-la-Neuve, Belgium)                                                                                            | 27       |

| 11:00-1:0 | )0 pm                                                    | LUNCH                                                                                                                                                                                                        |          |

| 1:00-1:40 | ) pm                                                     | "Large Scale Circuit Applications of SOI" (INVITED TALK)<br>Harold Hosack and SOI Project Team<br>(Texas Instruments, Dallas, TX)                                                                            | 29       |

| 1:40-4:00 | ) pm                                                     | SESSION II: DEVICE CHARACTERIZATION                                                                                                                                                                          | 30       |

|           |                                                          | Session Co-Chairmen: W. Krull and M. Duffy                                                                                                                                                                   |          |

| 2.1       | DLTS and Ta<br>P.K. McLard<br>(University<br>H.L. Hughes | n of SIMOX Processing and Device Performance by Combined<br>ransistor Analysis"<br>ty, B. Mazzari, S. Cristoloveanu and D.E. Ioannou<br>of Maryland, College Park, MD)<br>arch Laboratory, Washington, D.C.) | 31       |

| 2.2       | L.J. McDaid<br>(University<br>J.C. Alderr                | esistance in the Output Characteristics of SOI MOSFETs"<br>I, S. Hall and W. Eccleston<br>of Liverpool, Liverpool, United Kingdom)<br>nan<br>search, Northants, United Kingdom)                              | 33<br>35 |

| 2.3       | T.Elewa, B.<br>(INPG/ENSI<br>J. Davis                    | stigation of Edge Effects in SIMOX Transistors"<br>Kleveland, B. Boukriss, T. Ouisse, A. Chovet and S. Cristoloveanu<br>ERG, Grenoble, France)<br>ecom Research Labs, Ipswich, United Kingdom)               |          |

| 2:40-3:0  |                                                          | BREAK                                                                                                                                                                                                        |          |

2

-----

. .. .

| 2.4       | "Accumulation Leakage of SOI Back Channel Transistors with Total Dose Irradiation"<br>M.D. Jacunski and D.A. Adams<br>(Westinghouse Electric Corp., Baltimore, MD)<br>J.M. Hwang<br>(Westinghouse R&D Laboratory, Pittsburgh, PA)                                                           |    |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2.5       | "Comparison of Electrical Properties of SOS and ISE SOI Transistors"<br>E. Worley, J. Brandewie and P. Elkins<br>(Rockwell International, Newport Beach, CA)                                                                                                                                | 39 |  |

| 2.6       | "Electrical Characterization of SOS N-MOSFET's at Cryogenic Temperatures"<br>J. Wang, J. Chang, V.K. Raman and C.R. Viswanathan<br>(University of California, Los Angeles, CA)<br>P.K. Vasudev<br>(Sematech, Austin, TX)                                                                    | 41 |  |

| 4:00-7:30 | 0 pm Poster Session with Wine and Beer                                                                                                                                                                                                                                                      |    |  |

| 6:30-8:00 | 0 pm No-host Cocktail Bar                                                                                                                                                                                                                                                                   |    |  |

| 4:00-7:30 | 0 pm SESSION III: POSTER SESSION                                                                                                                                                                                                                                                            | 43 |  |

|           | Session Chairman: D. Ioannou                                                                                                                                                                                                                                                                |    |  |

| 3.1       | "Characterization of Negative Resistance and Bipolar Latchup in the SOI<br>Transistors by Two-Dimensional Numerical Simulation"<br>G. A. Armstrong<br>(Queen's University, Belfast, N. Ireland)<br>N.J. Thomas and J. R. Davis<br>(British Telecom Research Laboratories, Ipswich, England) | 44 |  |

| 3.2       | "On Double Surface Conduction in SOI MOSFETs"<br>J. Whitfield<br>(Motorola, Inc, Mesa, AZ)                                                                                                                                                                                                  | 46 |  |

| 3.3       | "Small Signal Modeling of MOSOS Capacitor"<br>M. Gaitan and P. Roitman<br>(National Institute of Standards and Technology, Gaitherburg, MD)                                                                                                                                                 | 48 |  |

| 3.4       | "Unexpected Effect in Conduction Characteristics of P <sup>+</sup> SOI Resistors<br>when Exposed to ESD"<br>E. R. Worley<br>(Rockwell International, Newport Beach, CA)                                                                                                                     | 50 |  |

| 3.5       | "Modes of Operation and Radiation Sensitivity of Ultrathin SOI Transistors"<br>D. C. Mayer<br>(Aerospace Corp., El Segundo, CA)                                                                                                                                                             | 52 |  |

.....

| 3.6  | "Minority Carrier Generation in Very Thin Silicon on Insulator Films"<br>T. Ouisse and T. Elewa<br>(LPCS Grenoble, France)<br>P. McLarty, S. Cristoloveanu and D. Ioannou<br>(University of Maryland, College Park, MD)<br>D. P. Vu<br>(KOPIN Corp., Taunton, MA) | 54 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.7  | "Characterization of MOSFETs on Very Thin SOI at Temperatures from 77K to 350K"<br>N. Kistler and J. Woo<br>(University of California, Los Angeles, CA)<br>K. Terrill<br>(IDT, Santa Clara, CA)<br>P. K. Vasudev<br>(Sematech, Austin, TX)                        | 56 |

| 3.8  | "Hydrogen as the Cause of Pit-Formation during Laser Recrystallization of<br>Silicon on Insulator Films"<br>G. J. Willems and H. E. Maes<br>(IMEC, Leuven, Belgium)                                                                                               | 58 |

| 3.9  | "Gettering of Threading Dislocations and Oxide Precipitates in SIMOX Material"<br>M. Tomozane and H. Ming Liaw<br>(Motorola Inc., Phoenix, AZ)                                                                                                                    | 60 |

| 3.10 | "Gallium Arsenide on Insulator by Electrostatic Bonding"<br>QA Huang, SJ. Lu and QY. Tong<br>(Southeast University, Nanjing, P. R. China)                                                                                                                         | 62 |

| 3.11 | "Fabrication of BESOI- Materials using Implanted Nitrogen as an Effective Etch<br>Stop Barrier"<br>A. Soderbarg<br>(Uppsala University, Uppsala, Sweden)                                                                                                          | 64 |

| 3.12 | "Critical Evaluation of Uniformity and Contamination in Porous Silicon SOI Wafers"<br>M.J. Kelly, T. R. Guilinger, S. S. Tsao, W. B. Chambers, G.J. Fisher and R. R. Sippio<br>(Sandia National Laboratories, Albuquerque, NM)                                    | 66 |

| 3.13 | "Gate Oxide Breakdown Behaviour in a Mesa SOI CMOS Process"<br>M. Haond, G. Mascarin and J. P. Gonchond<br>(CNET, Cedex, France)<br>O. Le Neel<br>(Matra-Harris Semiconducteurs, France)                                                                          | 68 |

| 3.14 | "Physical Characterization of Low Defect SIMOX Material"<br>P. S. Fechner, G. Gardner, J. Yue and S. T. Liu<br>(Honeywell SSEC, Plymouth, MN)<br>B. Cordts<br>(IBIS, Danvers, MA)                                                                                 | 70 |

| 3.15 | "Process Technology for 3D-CMOS Devices"<br>R. Buchner, K. Haberger, S. Seitz, J. Weber and P. Seegebrecht<br>(Fraunhofer-Institute fur Festkorpertechnologie, West Germany)<br>W. van der Wel<br>(Philips Research Laboratories, Hamburgy, W. Germany)           | 72 |

- -----

| 3.16 | "CMOS Devices Fabricated in Thin Epitaxial Silicon on Oxide"<br>D. L. Leung, R. C. Cole, D. M. Cobert, J. F. Knudsen, J. P. Hurrell<br>D. C. Mayer and R. Newman<br>(Aerospace Corp., El Segundo, CA)                                                                                                                     | 74 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.17 | "Quantitative Investigation of Impurity Distribution in ZMR SOI Layers"<br>P. W. Mertens and H. E. Maes<br>(IMEC, Leuven, Belgium)                                                                                                                                                                                        | 76 |

| 3.18 | "Observed Effects of Sapphire Substrate Preparation on the Subsequent<br>Electrical and Radiation Performance of CMOS/SOS Devices"<br>J. C. Black, P.P. Idell, P. M. Sandow and K. Strater<br>(GE Microelectronics Center, Research Triangle Park, NC)<br>M. Markette and R. Traczewski<br>(Union Carbide, Washougal, WA) | 78 |

| 3.19 | "Examination of Impurities in ISE <sup>TM</sup> SOI Material"<br>J. Knapp<br>(Sandia National Laboratory, Albuquerque, NM)<br>L. P. Allen and P. M. Zavracky<br>(KOPIN, Taunton, MA)                                                                                                                                      | 80 |

| 3.20 | "Effect of Annealing Conditions on Precipitate and Defect Evolution in<br>Oxygen Implanted SOI Material"<br>S. J. Krause and S. Visitserngtrakul<br>(Arizona State University, Tempe, AZ)<br>B. F. Cordts<br>(IBIS, Danvers, MA)<br>P. Roitman<br>(National Institue of Standards and Technology, Gaithersburg, MD)       | 81 |

| 3.21 | "An Electron Spin Resonance Study of ISE SOI Processed Structures"<br>P. M. Lenahan and G. A. Wilson<br>(Pennsylvania State University, University Park, PA)                                                                                                                                                              | 83 |

| 3.22 | "The Donor Concentration in Silicon Implanted Silicon and Silicon on Sapphire"<br>S. Peterson<br>(Chalmers University of Technology, Goteborg, Sweden)                                                                                                                                                                    | 85 |

| 3.23 | "Buried Oxide Leakage Current as a Function of Total Dose"<br>N. K. Annamalai<br>(Rome Air Development Center, Hanscom AFB,MA)<br>C. Surya and J. Chapski<br>(Northeastern University, Boston, MA)                                                                                                                        | 87 |

| 3.24 | "Technology Comparison (Bulk vs SIMOX vs SOS) of Interface States as<br>Measured by Charge Pumping"<br>R. K. Lawrence<br>(ARACOR, Washington, D.C.)<br>H.L. Hughes<br>(Naval Research Laboratory, Washington, D.C.)                                                                                                       | 89 |

- -

| 3. | .25 | "SIMS, DLTS, and Generation Lifetime Measurements of SIMOX Materials<br>Containing Metal Impurities"<br>J.M. Hwang                                                                                                                                                                     | 91  |

|----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|    |     | (Westinghouse R&D Center, Pittsburgh, PA)<br>D.A. Adams<br>(Westinghouse Electric Corp., Baltimore, MD)                                                                                                                                                                                |     |

| 3. | .26 | "Electrochemical Method for Defect Delineation in Thin-Film SOI Wafers"<br>T.R. Guilinger, M.J. Kelly, J.W. Medernach, S.S. Tsao, J.O. Steveson<br>and H.D.T. Jones<br>(Sandia National Laboratories, Albuquerque, NM)                                                                 | 93  |

| 3. | .27 | "Impact of Interface Preparation on Defect Generation during Wafer Bonding"<br>H. Baumgart, R.D. Pinker<br>(Philips Laboratories, Briarcliff Manor, NY)<br>E.F. Steigmeier, H. Auderset<br>(Paul Scherrer Inst., c/o RCA Laboratories, Zürich, Switzerland)                            | 95  |

|    |     | A.J.R. de Kock<br>(Philips Components, Nijmegen, Netherlands)                                                                                                                                                                                                                          |     |

| 3. | .28 | "Characterization of SIMOX and ZMR Materials by Spreading Resistance<br>and Point Contact Current Voltage Techniques"<br>P.C. Karulkar                                                                                                                                                 | 97  |

|    |     | (MIT Lincoln Laboratory, Lexington, MA)<br>R.J. Hillard and P. Rai-Choudhury<br>(Solid State Measurements, Inc., Pittsburgh, PA)                                                                                                                                                       |     |

| 3. | .29 | "Non-Destructive Characterization SIMOX Substrates"<br>B. Rod and R. Reams<br>(Harry Diamond Laboratory, Adelphi, MD)                                                                                                                                                                  | 99  |

| 3. | .30 | "An Evaluation of SOI Technologies for High Performance Analog Bipolar Circuits"<br>S.J. Gaul, J. A. Delgado, G.V. Rouse, C.J. McLachlan and W. A. Krull<br>(Harris Semiconductor, Melbourne, FL)                                                                                      | 101 |

| 3. | .31 | "Conversion of the PACE1750A CMOS Chip Set to Silicon on Sapphire"<br>M.D. Fitzpatrick, D.A. Adams, M. Austin, D.T. Uehara and K.A. Jones<br>(Westinghouse Electric Corp., Baltimore, MD)<br>R.R. Konegen, T.A. Longo and L.Sandman<br>(Performance Semiconductor Corp, Sunnyvale, CA) | 103 |

| 3. | .32 | "A 150-MHz 1.25 um CMOS/SOS DSP Integrated Circuit"<br>W.L. Marking, S.R. Powell, R.R. Siviy, W.S. Kephart and E.G. Friedman<br>(Hughes Aircraft Co., Carlsbad, CA)                                                                                                                    | 105 |

| 3. | .33 | "Analog CMOS/SOI with NMOS/SOI-Depletion Transistors"<br>A.G.F. Dingwall, FL. Hsueh and S.T. Hsu<br>(David Sarnoff Research Center, Princeton, NJ)                                                                                                                                     | 107 |

| 3. | .34 | "Novel Silicon-on-Insulator Structures for Silicon Waveguides"<br>E. Cortesi and F. Namvar<br>(Spire Corp, Bedford, MA)<br>R.A. Soref<br>(Rome Air Development Center, Hanscom AFB, MA)                                                                                                | 109 |

·····

· · · · - · · · - ·

| 3.35 | "Ultraviolet Reflectance of Room Temperature Nitrogen Implanted Silicon"<br>B. M. Lacquet and P. L. Swart<br>(Rand Afrikaans University, Johannesburg, South Africa)                                  | 110 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.36 | "X-ray Moire Pattern in Defect-Free Silicon-on-Insulator Wafer Prepared<br>by Oxygen Ion Implantation"<br>F. Shimura, B. L. Jiang and G. A Rozgonyi<br>(North Carolina State University, Raleigh, NC) | 112 |

5:00-6:30 pm <u>SEMI SOS Subcommittee Meeting</u>

#### Agenda:

- 1: Approval of minutes of October 3, 1988 in St. Simons Island, GA

- 2: Ballot: Secondary Flat Orientation

- 3: Task Force Report: Proposed Specifications for 125 and 150 mm diameter sapphire substrates

- 4: New Business

- 5: Next meeting date

8:00 pm

------

#### CONFERENCE BANQUET

### Banquet Speaker: Dr. John Moll Hewlett-Packard Laboratory Palo Alto, CA

### Wednesday, October 4

7:00-8:00 am Continental Breakfast

8:00-8:40 am "Limiting Factors for SOI VLSI High-Level Hardness: Modeling 114 and Improving" (INVITED TALK) Jean-Luc Leray, E. Dupont-Nivet, J. F. Pere. O Musseau, P. Lalande and A. Umbert (Commissariat a L'Energie Atomique, Bruyeres-le-Chatel, France)

## 8:40-10:20 am SESSION IV: MATERIALS FABRICATION 116

Session Chairmen: C. Hunt

4.1 "Low Energy SIMOX (LES)"

F. Namavar, E. Cortesi, B. Buchanan and P. Sioshansi (Spire Corp., Bedford, MA) 117

| 4.2      | "Seeded Lateral Epitaxial SOI Using (015) Substrate"<br>M. Maekawa, K. Shirakawa, T. Shinozaki, K. Ohtake and M. Koba<br>(SHARP Corp., Nara-city, Japan)                                                                        | 119 |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.3      | "A Comparison of Charge Transport in Electron-Beam and Graphite-Strip<br>ZMR"<br>H.J. Stein, L.R. Thompson and S.S. Tsao<br>(Sandia National Laboratory, Albuquerque, NM)                                                       | 121 |

| 4.4      | "Silicon Wafer Bonding: Chemistry, Elasto-Mechanics and Manufacturing"<br>R. Stengl, K. Mitani, V. Lehmann and U. Gosele<br>(Duke University, Durham, NC)                                                                       | 123 |

| 4.5      | "Generalized Wafer Bonding"<br>G. Goetz<br>(Allied-Signal Aerospace Technology Center, Columbia, MD)                                                                                                                            | 125 |

| 10:20-10 | :40 am <u>COFFEE BREAK</u>                                                                                                                                                                                                      |     |

| 10:40-12 | :00 pm SESSION V: DEVICE PROCESSING<br>Session Chairman: R. Reams                                                                                                                                                               | 127 |

| 5.1      | "Smart Body Contact for SOI MOSFETs"<br>M. Matloubian<br>(Texas Instruments, Dallas, TX)                                                                                                                                        | 128 |

| 5.2      | "P-poly and N-poly Gate Ultra-Thin Film SIMOX Transistors"<br>N.J. Thomas and J. R. Davis<br>(British Telecom Research Labs., Ipswich, England)                                                                                 | 130 |

| 5.3      | "Salicide (Self-Aligned Silicide) Technology for Ultra Thin SIMOX MOSFETs"<br>T. Nishimura, Y. Yamaguchi, H. Miyatake and Y. Akasaka<br>(Mitsubishi Electric Corp., Itami, Japan)                                               | 132 |

| 5.4      | "Dual-Gate SOI CMOS Technology by Local Overgrowth (LOG)"<br>R.P. Zingg, B. Hofflinger<br>(Institute for Microelectronics, Stuttgart, FRG)<br>G.W. Neudeck<br>(Purdue University, W. Lafayette, IN)                             | 134 |

| 12:00 no | on LATE NEWS                                                                                                                                                                                                                    | 136 |

|          | Session Chairman: G. E. Davis                                                                                                                                                                                                   |     |

| L1       | "1 um CMOS/SOI 64K SRAM with 10 nA Standby Current"<br>T.W. Houston, H. Lu, P. Mei, T.G.W. Blake, L.R. Hite, R. Sundaresan,<br>M.Matloubian, W.E. Bailey, J. Liu, A. Peterson and G. Pollack<br>(Texas Instruments, Dallas, TX) | 137 |

· · · · · ·

. . .

| L2        | G.K. Celler,<br>W.S. Lindenb<br>(ATT Bell La<br>J. C. Sturm              | Digital CMOS Circuit in Thin SIMOX Films"<br>HI. Cong, R.L. Field, S.J. Hillenius, A. Kamgar,<br>perger, L. E. Trimble<br>abs, Murray Hill, NJ)<br>fniversity, Princeton, NJ)                             | 139 |

|-----------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| L3        | Film SOI-MC<br>H. Aoki, H. C                                             | ulation of 0.1 um Gate-Length, 77K Operated, Ultra-Thin<br>OSFETs"<br>Okabayashi and T. Mogami<br>ration, Kawasaki, Japan)                                                                                | 141 |

| L4        | D. Godbey, H<br>(Naval Resea<br>M. Twigg<br>(GEO-Center<br>L. Palkuti, P | Strained Layer Etch Stop for the Generation of Bond<br>Ck SOI"<br>I. Hughes and F. Kub<br>arch Laboratory, Washington, D.C.)<br>rs, Inc., Fort Washington, MD)<br>J. Leonov and J. Wang<br>Sunnyvale, CA) | 143 |

| 12:30 pm  |                                                                          | LUNCH                                                                                                                                                                                                     |     |

|           |                                                                          | Afternoon Free                                                                                                                                                                                            |     |

| 5:30-6:00 | pm                                                                       | No-host Cocktail Bar                                                                                                                                                                                      |     |

| 6:00-8:00 | pm                                                                       | Cookout                                                                                                                                                                                                   |     |

| 8:00-11:0 | 0 pm                                                                     | RUMP SESSION                                                                                                                                                                                              |     |

| Thursday  | <u>, October 5</u>                                                       |                                                                                                                                                                                                           |     |

| 7:00-8:00 | am                                                                       | Continental Breakfast                                                                                                                                                                                     |     |

| 8:00-8:40 | am                                                                       | "Design and Applications of Ultra-thin SOI MOSFETs"<br>(INVITED TALK)<br>Makoto Yoshimi<br>(Toshiba Corp., ULSI Research Center, Kawasaki, Japan)                                                         | 145 |

· · · ·

| 8:40-1 | :40 am SESSION VI: MATERIALS CHARACTERIZATION                                                                                                                                                                                                                                                                                | 147 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|        | Session Co-Chairmen: S.S. Tsao and J. Schott                                                                                                                                                                                                                                                                                 |     |

| 6.1    | "Detailed Charge Pumping Evaluation of SIMOX Using Gated P-I-N Diodes"<br>T. Ouisse, T. Elewa and S. Cristoloveanu<br>(LPCS/ENSERG, Grenoble-Cedex, France)<br>H. Haddara<br>(Ain-Shams University, Cairo, Egypt)<br>G. Borel<br>(Thomson TMS, Grenoble, France)<br>D. Ioannou<br>(University of Maryland, College Park, MD) | 148 |

| 6.2    | "Characterization of <sup>28</sup> Si <sup>+</sup> Implantation Induced Damage in SIMOX"<br>J.F. Knudsen, P.M. Adams, R.C.Bowman, Jr., D.D. Smith and S.C. Moss<br>(Aerospace Corp., El Segundo, CA)                                                                                                                         | 150 |

| 6.3    | "Quantitative Measurement of Surface, Trace Metal Contamination on SOS/SOI<br>Using Total Reflection X-ray Fluorescence (TXRF)"<br>R. S. Hockett<br>(Charles Evans & Assoc., Redwood City, CA)<br>R.G. Wilson<br>(Hughes Research Labs, Malibu, CA)                                                                          | 152 |

| 6.4    | "Materials and Processing Parameters Effecting the Radiation Tolerance<br>of SIMOX Devices"<br>A.C. Ipri, L. L. Jastrzebski, D. Peters and S. Policastro<br>(David Sarnoff Research Center, Princeton, NJ)                                                                                                                   | 154 |

| 10:00- | 10:20 am <u>BREAK</u>                                                                                                                                                                                                                                                                                                        |     |

| 6.5    | "A Detailed Study of Buried Oxide Charge as a Function of Processing<br>and Irradiation"<br>F. T. Brady, S.S. Li<br>(University of Florida, Gainesville, FL)<br>W.A. Krull<br>(Harris Semiconductor, Melbourne, FL)                                                                                                          | 156 |

| 6.6    | "Silicon and Insulator Thickness Estimation in SOI by Means of Spectral<br>Estimators Applied to Transformed Infrared Reflectance Data"<br>P. L. Swart and B. M. Lacquet<br>(Rand Afrikaans University, Johannesburg, South Africa)                                                                                          | 158 |

| 6.7    | "Optical Waveguides and SIMOX Characterization"<br>D.E. Davies<br>(EOARD, London, England)<br>M. Burnham<br>(Motorola, Phoenix, AZ)<br>T.M. Benson, N.M. Kassim<br>(University of Nottingham, Nottingham, England)<br>M. Seifouri<br>(Brighton Polytechnic, England)                                                         | 160 |

•

•···•

| 6.8       | "Reassessment of Defect Models in Graphite Strip Heater Zone-Melt 16<br>Recrystallized Material by Non-Destructive Thin Film Diagnostics"<br>M.J.J. Theunissen, A.H. Goemans, A.J.R. de Kock, M.L.J. Geijselaers and<br>H. Baumgart<br>(Philips Research Laboratories, Endhoven, Netherlands) |                                                                                                                                                                                          |     |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 11:40-1:0 | 00 pm                                                                                                                                                                                                                                                                                         | LUNCH                                                                                                                                                                                    |     |

| 1:00-3:20 | 0 pm                                                                                                                                                                                                                                                                                          | SESSION VII: ADVANCED CIRCUIT APPLICATIONS                                                                                                                                               | 164 |

|           |                                                                                                                                                                                                                                                                                               | Session Co-Chairmen: R. Sundaresan and J. Brandewie                                                                                                                                      |     |

| 7.1       | D.P. Vu, M.<br>(Kopin Corp<br>D.A. Adams                                                                                                                                                                                                                                                      | erature Operation of ISE Devices and Circuits"<br>J. Boden, W.R. Henderson, N.K. Cheong and P.M. Zavracky<br>J., Taunton, MA)<br>S and M.M. Austin<br>Ise Electric Corp., Baltimore, MD) | 165 |

| 7.2       | Hard Comp<br>W. Walker,                                                                                                                                                                                                                                                                       | Analysis of a CMOS SOS/SOI Clock Reciever for a Radiation<br>uter"<br>H. Lane and E. Worley<br>nternational, Newport Beach, CA)                                                          | 167 |

| 7.3       | Speed Appli<br>A.J. Aubert                                                                                                                                                                                                                                                                    | ces of a 16K SRAM Processed in a 150 nm SIMOX Film for High<br>ications"<br>con-Herve, B. Giffard and M. Bruel<br>TI, Grenoble-Cedex, France)                                            | 169 |

| 7.4       | T.W. MacEl                                                                                                                                                                                                                                                                                    | tion Mode Transistors for Silicon-on-Insulator Circuits"<br>wee and I.D. Calder<br>'elecom Electronics, LTD, Ottawa, Canada)                                                             | 171 |

| 7.5       | Substrates<br>W.F. Kraus                                                                                                                                                                                                                                                                      | Configuration 1.2 micron 64K SRAM Fabricated on SIMOX<br>with Laser Link Redundancy"<br>and J.C. Lee<br>niconductor, Melbourne, FL)                                                      | 173 |

| 7.6       | on Bonded,<br>M. C. Churo                                                                                                                                                                                                                                                                     | ative Study of Functional 16K Bipolar PROM Circuits Fabricated<br>Oxide Isolated and Junction Isolated Substrates"<br>ch<br>niconductor, Melbourne, FL)                                  | 175 |

| 7.7       | and Logic C<br>R. C. Heune                                                                                                                                                                                                                                                                    | OS Process for High Reliability, Radiation Hard, High Speed Memories<br>Circuits<br>er, M.S. Hwang and O. Bismarck<br>hiconductor, Somerville, NJ)                                       | 177 |

.

3:20 pm CONCLUDING REMARKS: J.-P. Colinge

-----

Substrate Bias and Temperature Dependence of Anomalous Subthreshold Slopes in Fully-Depleted Submicron SOI MOSFET's

K. Tokunaga\* and J.C. Sturm Department of Electrical Engineering Princeton University, Princeton, N.J. 08544

J-P. Colinge IMEC, B-3030 Leuven, Belgium

\* Present address: Semiconductor Design & Development Ctr., Hitachi Ltd., Tokyo 187, Japan

Recently, anomalously sharp subthreshold slopes have been reported in non-fully depleted short-channel SOI MOSFET's [1,2]. Since this effect varies with drain voltage and can cause excessive leakage currents in circuit operation, it could be a serious impediment to the widespread use of SOI for VLSI applications. We here report observation of the effect in fully-depleted ultra-thin SOI MOSFET's, but have found that it can be eliminated by control of the lower SOI interface charge condition. The temperature dependence of this effect has also been investigated.

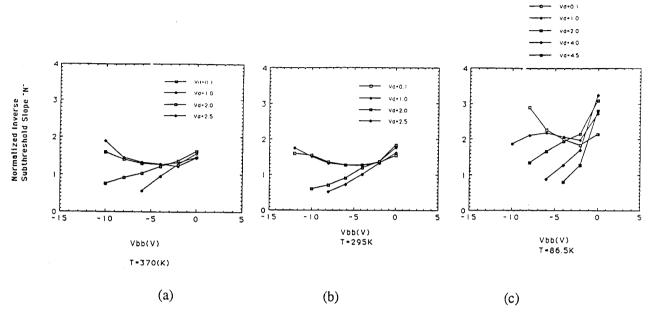

Classically, the subthreshold slope of a MOSFET is independent of drain voltage, with an optimum value of  $kT/q \ln(10)$  /decade, corresponding to 59 mV/decade at room temperature. One expects to measure this ideal value when there are no parasitic capacitances coupling to the channel. In fig. 1 is shown the normalized subthreshold slope "n" (measured slope/ideal value) as a function of drain voltage and substrate bias of 0.8-µm n-channel SOI FET's for temperatures from 86 K to 370 K. The 1000-Å SOI films were formed by oxygen implantation and relatively low temperature (1250 C) annealing. The gate oxide thickness was 250 Å, and the film doping was chosen to yield full depletion during FET operation. At all temperatures, several universal trends are noted.

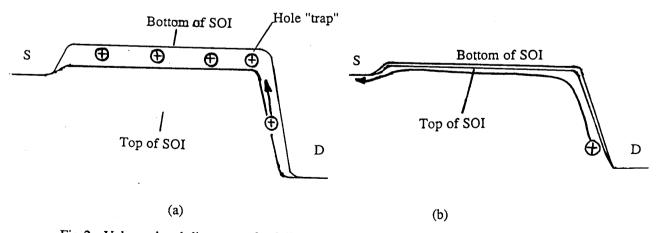

First, for  $V_D = 0.1$  V, a minimum subthreshold slope is consistently observed for  $V_{BB}$  (substrate bias) of about - 3 V, increasing to a much larger value for  $V_{BB} = -10$  V. Separate measurements of threshold voltage vs. substrate bias show that -3 V corresponds to full depletion of the SOI film and lower interface. In this condition parasitic channel capacitances are minimized, and an optimum substhreshold slope is indeed expected [3]. For a substrate bias of -10 V, the lower SOI interface is accumulated, pinning the backside potential and introducing a parasitic channel capacitance. Calculations based on a simple capacitor model predict a "n" of 1.8 in this case, in good agreement with experiment. For substrate biases more positive than -3V, conduction in the lower SOI channel becomes significant. This current is not as efficiently modulated by the front gate voltage, resulting in a degradation of subthreshold slope in all cases.

The subthreshold slope for  $V_D = 0.1 \text{ V}$  scales well with temperature from 200K to 370 K, with a constant minimum "n", as expected from simple theory. The minimum "n" of 1.3 is consistent with an interface state density of about  $10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$ . At 86 K, the minimum n increases to 1.9. This could be caused by a surface potential fluctuation in space which would be insignificant at larger kT.

For larger drain voltages, the subthreshold slopes are virtually unchanged in the case of full depletion at the lower SOI interface. However, a radical drop in subthreshold slope is seen when the substrate bias is decreased below -3V. Although the SOI film body is depleted, accumulation at the lower SOI interface causes an effective hole "trap" to be present in the band diagram at the lower interface. Holes injected into the SOI film from thermal leakage or avalanche at the drain junction will be trapped, leading to a positive SOI body bias and increased current. This multiplication mechansism leads to the anomalously sharp slopes, exactly as in thicker non-fully depleted films [2]. When the lower interface is fully depleted, the hole "trap" is removed from the band diagram, inhibiting the multiplication mechanism and the anomalous slopes. Since the anomalous slopes can lead to increased leakage in circuits, the fully-depleted operating condition is the optimum design condition for VLSI operation. The support of Hewlett Packard, Rucker and Kolls, and IBM is acknowledged.

1. J.R. Davis, A.E. Glaccum, K. Reeson, and P.L.F. Hemment, IEEE Elec. Dev. Lett. EDL-7, 570-572 (1986).

2. J.G. Fossum, R.Sundaresan, and M.Matloubian, IEEE Elec. Dev. Lett. EDL-8, 544-546 (1987).

3. J-P. Colinge, IEEE Elec. Dev. Lett. EDL-7, 244-246 (1986).

Fig. 1. Drain voltage and substrate bias dependence of normalized subthreshold slope at 370 K, 295 K, and 86 K.

Fig 2. Valence band diagrams of a fully-depleted SOI MOSFET in subthreshold with (a) an accumulated lower interface, and (b) a depleted lower interface.